# Help Volume

$\ \, {\mathbb C}$  1992-2002 Agilent Technologies. All rights reserved.

System: Measurement Examples

# **Measurement Examples**

These quick reminders on how to perform common measurements are grouped by the development phase in which the measurement typically occurs:

- "Hardware Turn-On" on page 10 Hardware designers take a loaded first cut printed-circuit board and verify its basic operation before delivering it to driver writers and software developers.

- "Firmware Development" on page 143 Given a printed-circuit board that has been turned-on, firmware developers create drivers and operating system calls that control and communicate with the hardware. They deliver stable hardware with a low-level software interface to application software developers.

- "Software Development" on page 198 Given stable hardware and lowlevel driver software, software developers verify real-time application software execution.

- "System Integration" on page 257 When system problems are discovered, system integrators determine whether the problem is being caused by hardware, software, or both. Also, they analyze system performance.

#### See Also

"Contents" on page 6

"Measurement Tips & Tricks" on page 300

Main System Help (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume)

Glossary (see page 311)

# Contents

# **Measurement Examples**

## 1 Measurement Examples

Contents 6

Hardware Turn-On 10

Looking at Signal Parameters 11

Looking at Signal Edges, Patterns, and Glitches 16

Measuring Conformance to Specifications 50

Looking at State Events 96

Exercising the Microprocessor (with the Emulation Probe) 136

Firmware Development 143

Testing Boot Code (with the Emulation Probe) 143

Making Driver Development Measurements 155

Making Interrupt Service Routine Measurements 183

Software Development 198

Analyzing Real-Time Software Execution 198

Analyzing Real-Time Variable Access 229

Analyzing Real-Time Memory Usage 250

System Integration 257

Making Cross-Domain Measurements 257

Making System Profile Measurements 282

Isolating Critical Defects 288

# Contents

Measurement Tips & Tricks 300

Setting up 16715/16/17/18/19A triggers 300

Setting up triggers in other logic analyzers 302

Use trigger functions for easy measurement set up 305

Modify trigger functions to build new measurements 307

Know how processor execution affects measurements 308

Getting the most out of trace memory 309

If the trigger doesn't occur as expected 309

# Glossary

# Index

1

Measurement Examples

# Contents

#### Hardware Turn-On

Looking at Signal Parameters

• "To make basic oscilloscope measurements" on page 11

Looking at Signal Edges, Patterns, and Glitches

- "To trigger on a stable pattern" on page 16

- "To find edges that are too close or too far" on page 20

- "To find the Nth transition of a signal" on page 24

- "To find when a signal or pattern stops" on page 28

- "To delay capture after a pattern" on page 32

- "To find an edge during a valid pattern" on page 36

- "To find a pattern, an edge, and another pattern" on page 40

- "To find signal glitches" on page 45

Measuring Conformance to Specifications

- "To measure conformance to specs (with the Compare tool)" on page 51

- "To find setup and hold violations" on page 56

- "To trigger if a pattern doesn't follow an edge" on page 59

- "To verify pulse widths" on page 63

- "To trigger on a violation of an edge sequence" on page 67

- "To trigger when two edges are asserted simultaneously" on page 71

- "To generate pattern stimulus on devices" on page 75

- "To analyze jitter or time dispersion (with SPA)" on page 81

- "To analyze bus stability (with SPA)" on page 88

Looking at State Events

• "To trigger on the Nth occurrence of an event" on page 96

- "To store N samples of an event" on page 100

- "To trigger on a sequence of events" on page 105

- "To trigger when a program loop exits" on page 111

- "To find events that are too close or too far" on page 116

- "To count occurrences of an event between two events" on page 120

- "To trigger on a function call sequence" on page 125

- "To analyze bus occupation & bandwidth (with SPA)" on page 131

Exercising the Microprocessor (with the Emulation Probe)

- "To initialize registers, access memory" on page 137

- "To use the emulation probe as a test tool" on page 140

# Firmware Development

Testing Boot Code (with the Emulation Probe)

- "To download boot code" on page 144

- "To start or stop processor execution" on page 147

- "To stop processor execution using breakpoints" on page 149

- "To capture startup execution" on page 152

Making Driver Development Measurements

- "To trigger on an 8-bit serial pattern" on page 155

- "To view serial data in parallel" on page 160

- "To capture driver execution (& view HW and SW)" on page 165

- "To capture execution up to a failure or halt" on page 171

- "To view bus activity" on page 174

- "To capture simple program messages" on page 175

- "To trigger on packet data (with DataComm Analysis)" on page 177

Making Interrupt Service Routine Measurements

• "To capture interrupt frequency and type" on page 183

- "To measure interrupt latency and execution time" on page 186

- "To simulate particular interrupt sequences" on page 191

- "To view the occurrence rate of an event (with SPA)" on page 192

## Software Development

#### Analyzing Real-Time Software Execution

- "To trace about a source line" on page 199

- "To trace function flow" on page 203

- "To trace callers of a function" on page 206

- "To trace execution within a function" on page 210

- "To measure function execution time" on page 214

- "To measure function execution time (with SPA)" on page 218

- "To omit monitor cycles from the trace" on page 223

- "To stop execution at a source line (in ROM)" on page 226

#### Analyzing Real-Time Variable Access

- "To find NULL pointer de-references" on page 229

- "To trace a variable's values" on page 231

- "To find where variables are accessed from" on page 236

- "To trace before a variable value" on page 240

- "To stop execution on a corrupt variable" on page 245

#### Analyzing Real-Time Memory Usage

- "To monitor stack or heap usage" on page 251

- "To find stack overflow or guarded memory access" on page 255

## **System Integration**

#### Making Cross-Domain Measurements

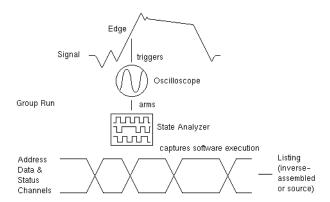

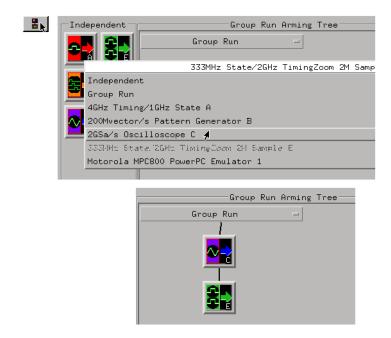

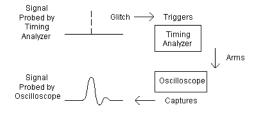

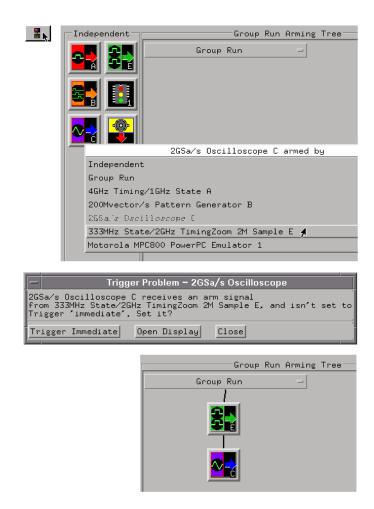

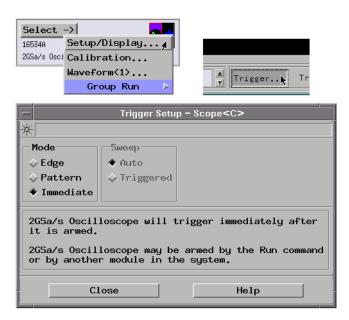

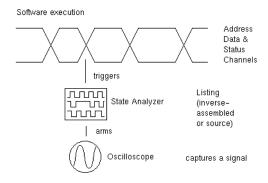

- "To capture software execution when a scope triggers" on page 258

- "To generate patterns when a source line executes" on page 262

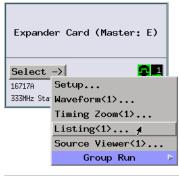

- "To arm one logic analyzer with another's trigger" on page 266

- "To arm a state machine with a timing machine trigger" on page 271

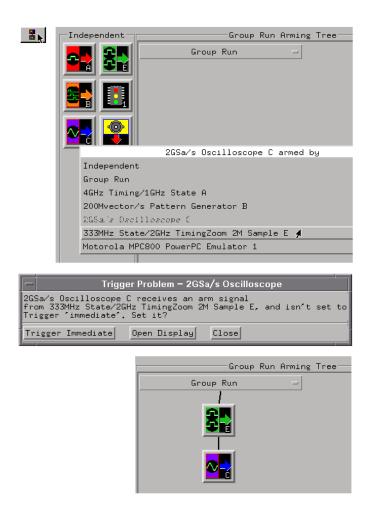

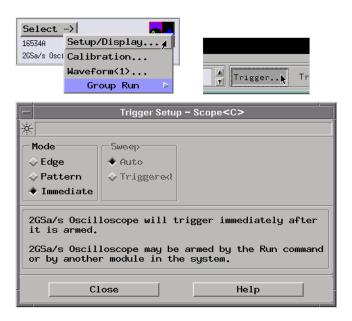

- "To arm an oscilloscope when the analyzer triggers" on page 277

### Making System Profile Measurements

- "To isolate the root cause of a performance bottleneck" on page 283

- "To simulate bus occupation and measure SW performance" on page 287

#### **Isolating Critical Defects**

- "To capture SW execution on a setup or hold violation" on page 289

- "To trigger an oscilloscope when a source line executes" on page 294

# Measurement Tips & Tricks

- "Setting up 16715/16/17/18/19A triggers" on page 300

- "Setting up triggers in other logic analyzers" on page 302

- "Use trigger functions for easy measurement set up" on page 305

- "Modify trigger functions to build new measurements" on page 307

- "Know how processor execution affects measurements" on page 308

- "Getting the most out of trace memory" on page 309

- "If the trigger doesn't occur as expected" on page 309

# Hardware Turn-On

Looking at Signal Parameters

- "To make basic oscilloscope measurements" on page 11

- Looking at Signal Edges, Patterns, and Glitches

- "To trigger on a stable pattern" on page 16

- "To find edges that are too close or too far" on page 20

- "To find the Nth transition of a signal" on page 24

- "To find when a signal or pattern stops" on page 28

- "To delay capture after a pattern" on page 32

- "To find an edge during a valid pattern" on page 36

- "To find a pattern, an edge, and another pattern" on page 40

- "To find signal glitches" on page 45

## Measuring Conformance to Specifications

- "To measure conformance to specs (with the Compare tool)" on page 51

- "To find setup and hold violations" on page 56

- "To trigger if a pattern doesn't follow an edge" on page 59

- "To verify pulse widths" on page 63

- "To trigger on a violation of an edge sequence" on page 67

- "To trigger when two edges are asserted simultaneously" on page 71

- "To generate pattern stimulus on devices" on page 75

- "To analyze jitter or time dispersion (with SPA)" on page 81

- "To analyze bus stability (with SPA)" on page 88

## Looking at State Events

• "To trigger on the Nth occurrence of an event" on page 96

- "To store N samples of an event" on page 100

- "To trigger on a sequence of events" on page 105

- "To trigger when a program loop exits" on page 111

- "To find events that are too close or too far" on page 116

- "To count occurrences of an event between two events" on page 120

- "To trigger on a function call sequence" on page 125

- "To analyze bus occupation & bandwidth (with SPA)" on page 131

Exercising the Microprocessor (with the Emulation Probe)

- "To initialize registers, access memory" on page 137

- "To use the emulation probe as a test tool" on page 140

# Looking at Signal Parameters

"To make basic oscilloscope measurements" on page 11

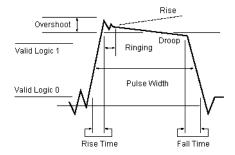

# To make basic oscilloscope measurements

#### Possible uses:

- To measure the analog parameters of signals.

- To trace to the root cause of noise, crosstalk, or ground bounce problems when combined with a logic analyzer.

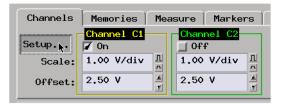

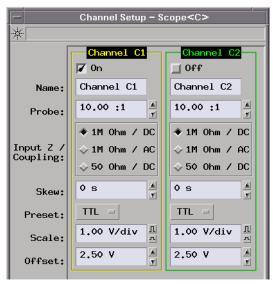

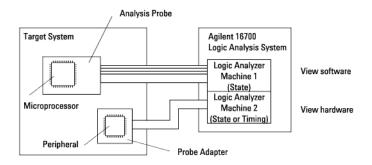

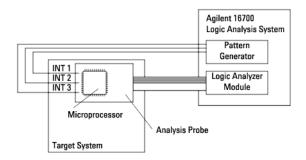

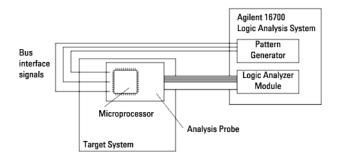

## Probing the Target System

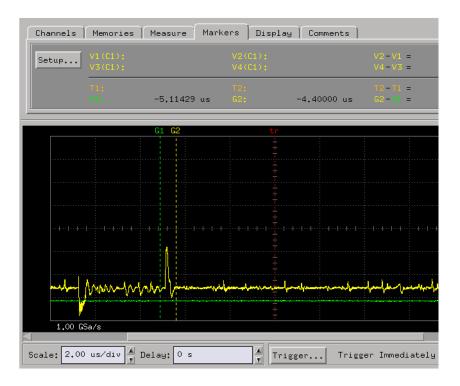

- 1. Connect the oscilloscope channel probes to signals of interest in the target system.

- 2. Display the oscilloscope window.

3. Select the Channels tab, and set up the channels.

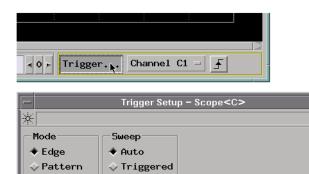

#### **Capturing the Data**

1. Set up the trigger.

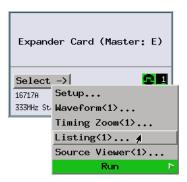

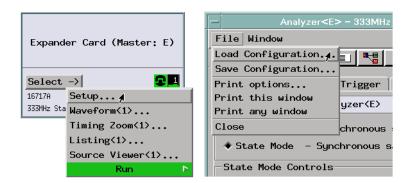

2. Select the Run button to capture an oscilloscope trace.

Level:

1.62 V

You may want to change the time/div scale and select the Run button again to capture data with a different sample rate.

Slope: Occurrences:

Immediate

Channel C1 =

Source:

# **Displaying the Data**

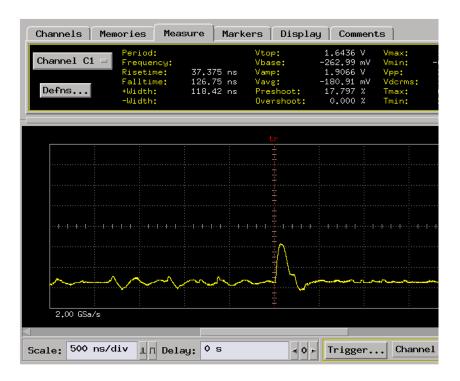

1. Select the Measure tab to view the data on the analog parameters of the captured signal.

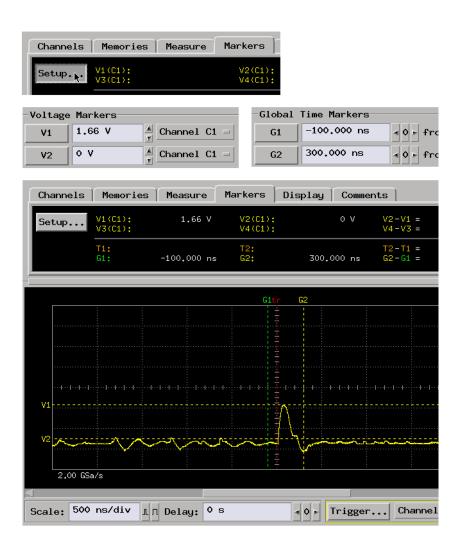

2. Select the Markers tab to set up voltage and time markers on the display.

#### See Also

"To capture software execution when a scope triggers" on page 258 "To arm an oscilloscope when the analyzer triggers" on page 277 "To trigger an oscilloscope when a source line executes" on page 294

# Looking at Signal Edges, Patterns, and Glitches

- "To trigger on a stable pattern" on page 16

- "To find edges that are too close or too far" on page 20

- "To find the Nth transition of a signal" on page 24

- "To find when a signal or pattern stops" on page 28

- "To delay capture after a pattern" on page 32

- "To find an edge during a valid pattern" on page 36

- "To find a pattern, an edge, and another pattern" on page 40

- "To find signal glitches" on page 45

# To trigger on a stable pattern

#### Possible uses:

- To wait for all status lines to finish transitioning before triggering.

- To filter out spurious triggers because of transitions that occur when the target system's state machine is indeterminate.

## Probing the Target System

- 1. Connect the logic analyzer probes to the signals on which you will look for the pattern.

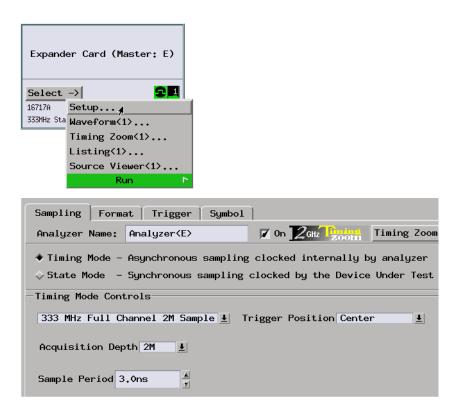

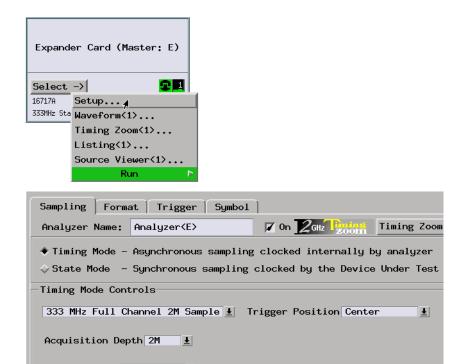

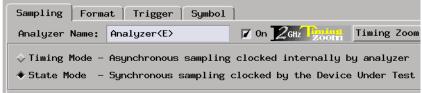

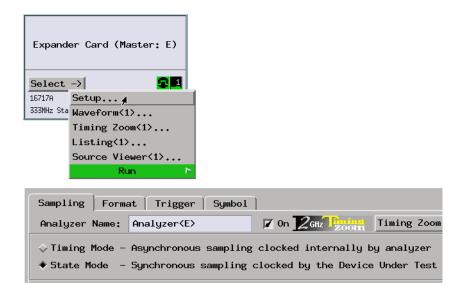

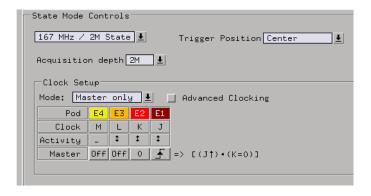

- 2. Configure a timing analysis machine.

3. Assign pods if necessary.

4. Format a label for the signals on which you will look for a stable pattern.

#### Capturing the Data

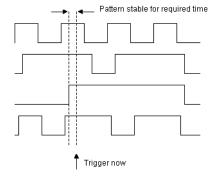

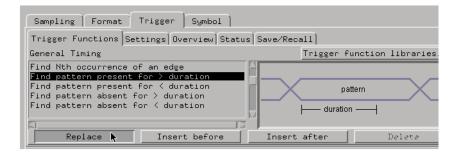

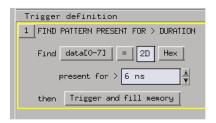

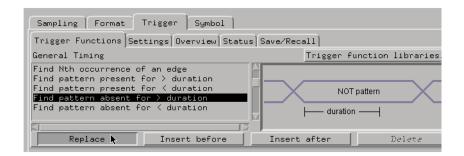

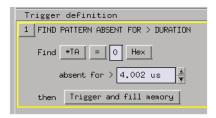

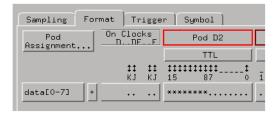

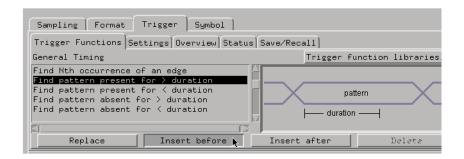

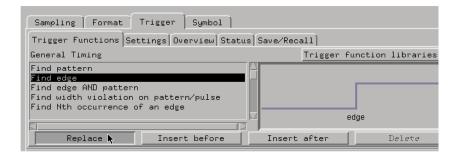

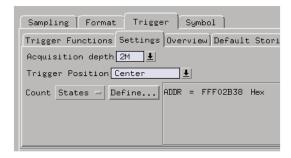

1. Use the "Find pattern present for > duration" trigger function.

2. In the trigger definition, specify the pattern, and enter the time that pattern must be stable for.

3. Select the Run button to start the measurement.

## **Displaying the Data**

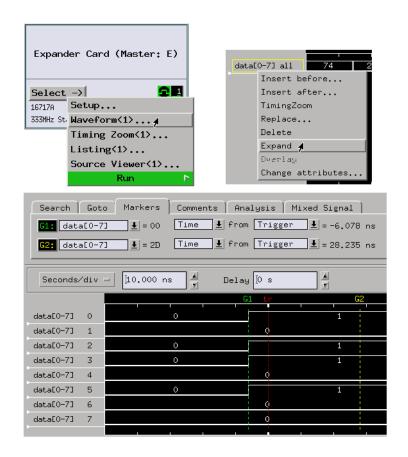

1. Use the Waveform display to verify that the pattern was stable for the specified time before the trigger.

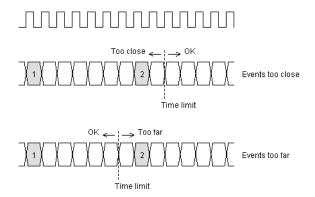

# To find edges that are too close or too far

# Possible uses:

To check DRAM row/column address strobe timing.

# Probing the Target System

- 1. Connect logic analyzer probes to the signals whose edges you wish to look at.

- 2. Configure a timing analysis machine.

3. Assign pods if necessary.

4. Format labels for the signals of interest.

# **Capturing the Data**

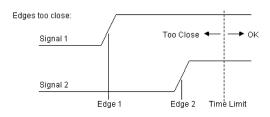

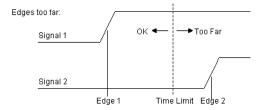

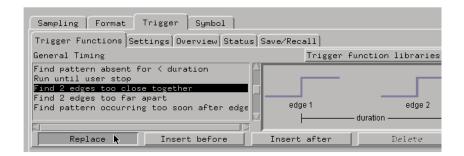

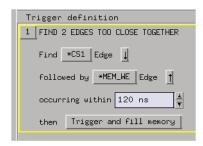

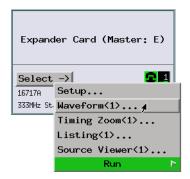

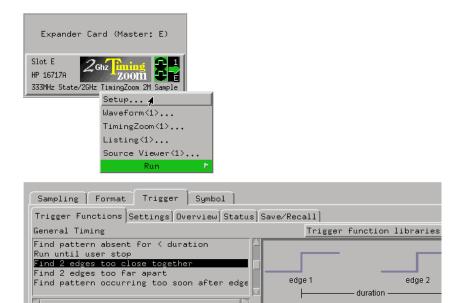

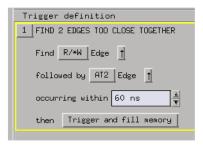

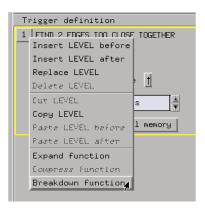

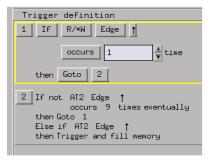

1. Use the "Find 2 edges too close together" or the "Find 2 edges too far apart" trigger function.

2. In the trigger definition, select edges and time.

3. Select the Run button to start the measurement.

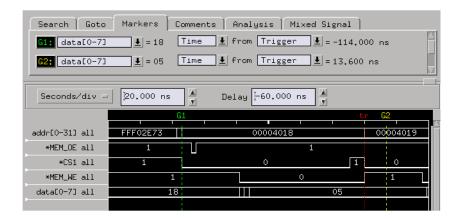

# **Displaying the Data**

1. Open the Waveform display and use the global markers to show the time between the edges.

#### See Also

"Use trigger functions for easy measurement set up" on page 305

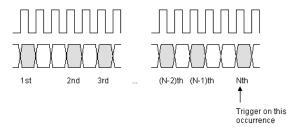

# To find the Nth transition of a signal

#### Possible uses:

- To find the 3rd occurrence of the start of a data transfer.

- To find the 1000th occurrence of a chip select line being asserted.

## Probing the Target System

- $1. \ \ Connect\ a\ logic\ analyzer\ probe\ to\ the\ signal\ of\ interest.$

- 2. Configure a timing analysis machine.

3. Assign pods if necessary.

4. Format labels for the signals of interest.

# **Capturing the Data**

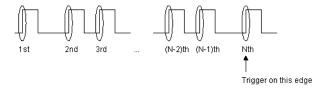

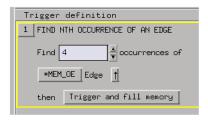

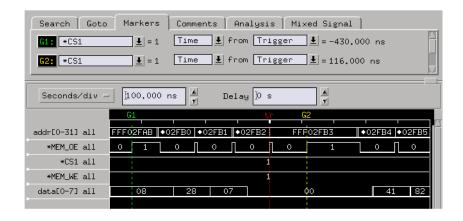

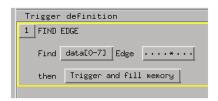

1. Use the "Find Nth occurrence of an edge" trigger function.

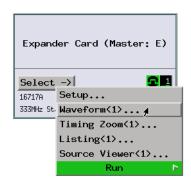

2. In the trigger definition, select the edge label and number of occurrences.

3. Select the Run button to start the measurement.

# **Displaying the Data**

1. In the Waveform window (depending on the time between signal transitions) you may be able to see that you've triggered on the Nth transition of the signal.

#### See Also

"Use trigger functions for easy measurement set up" on page 305

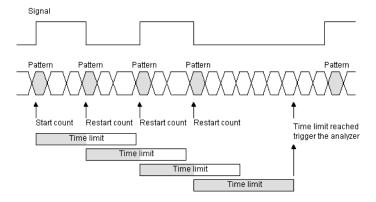

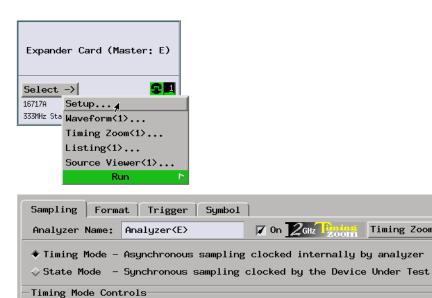

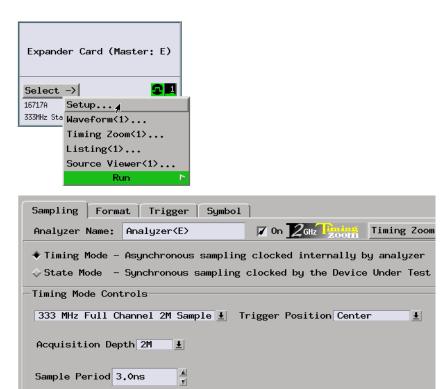

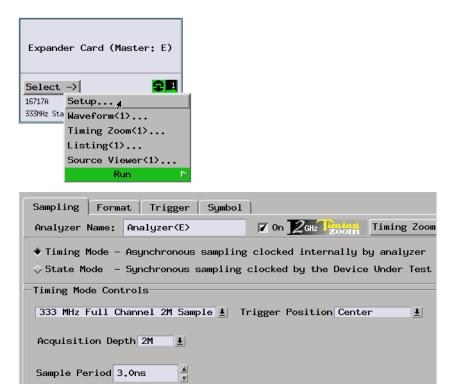

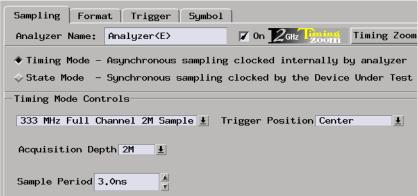

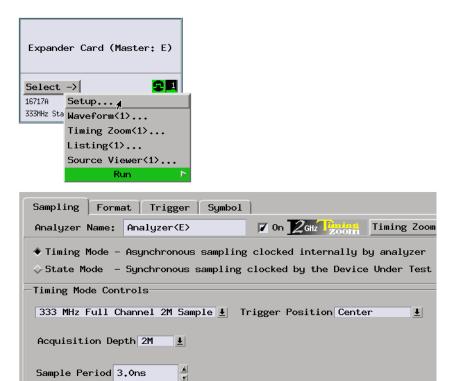

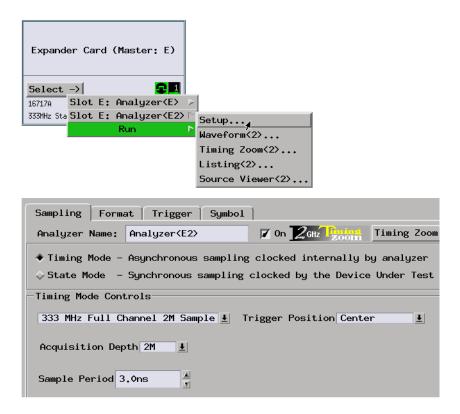

# To find when a signal or pattern stops

You can count time by counting occurrences of sampled data or by using a timer.

#### Possible uses:

- To find when signals are inactive for too long a time.

- To check when execution leaves an address range.

- To check when expected variable values stop being written.

To capture what leads up to an unexpected condition.

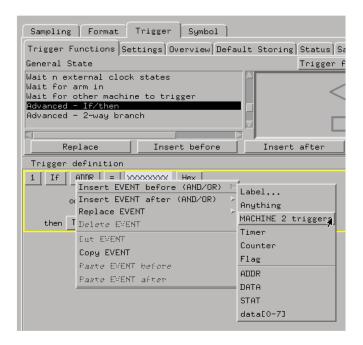

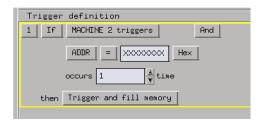

## **Probing the Target** System

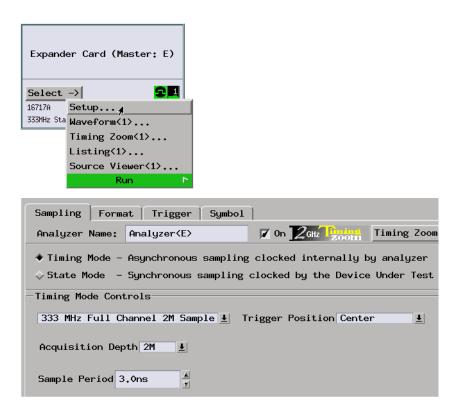

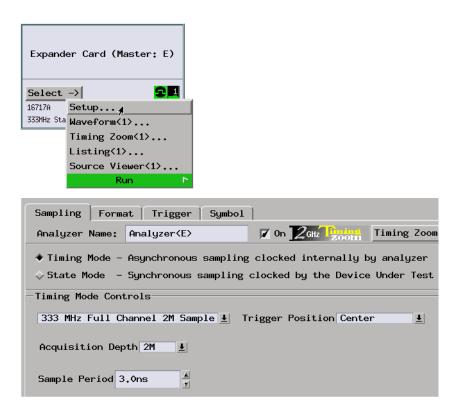

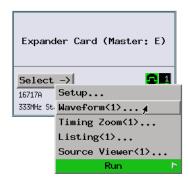

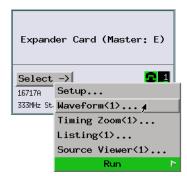

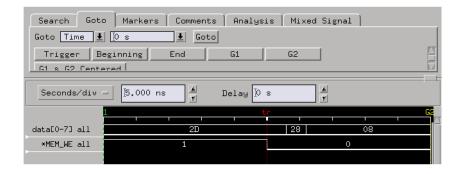

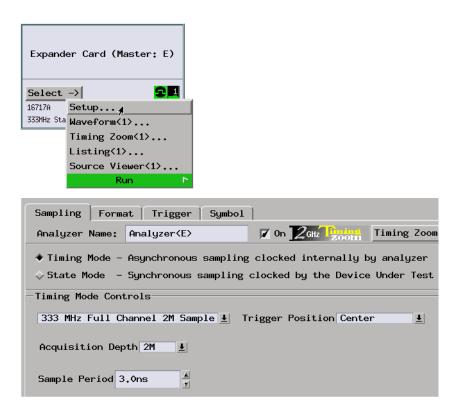

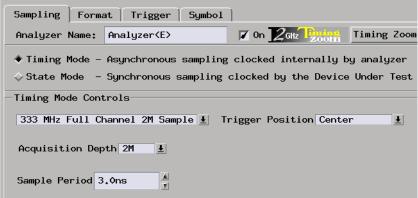

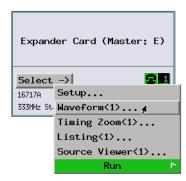

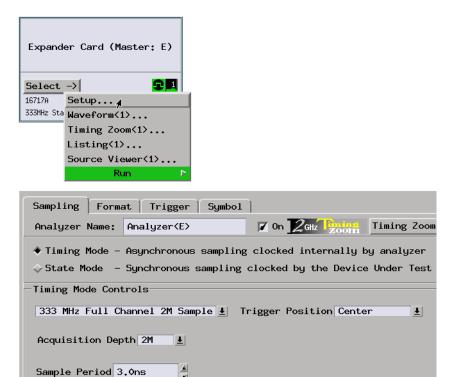

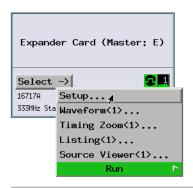

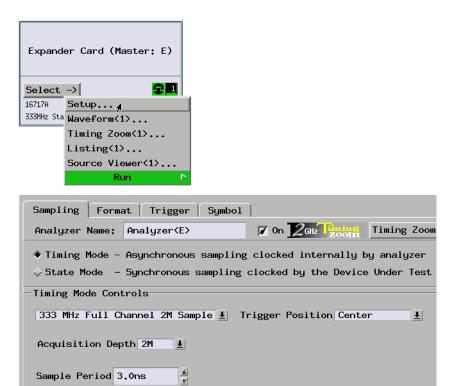

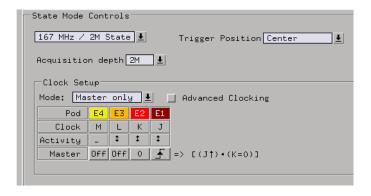

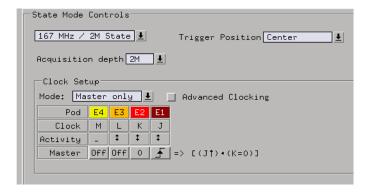

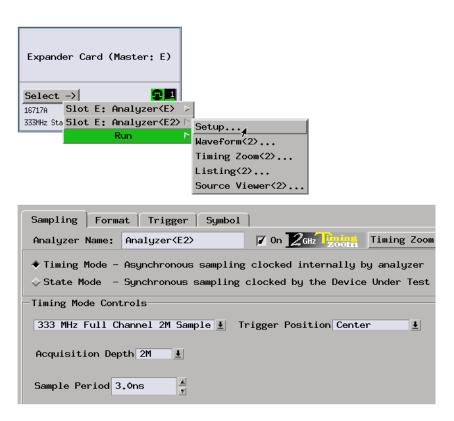

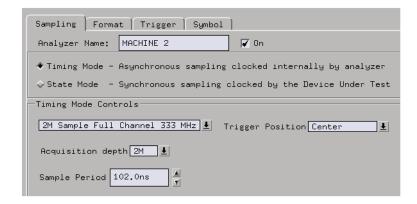

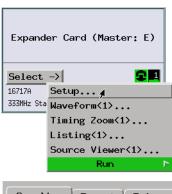

1. Configure a timing machine to look at signal edges or patterns.

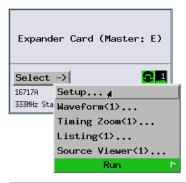

333 MHz Full Channel 2M Sample

▼ Trigger Position Center

<u>+</u>

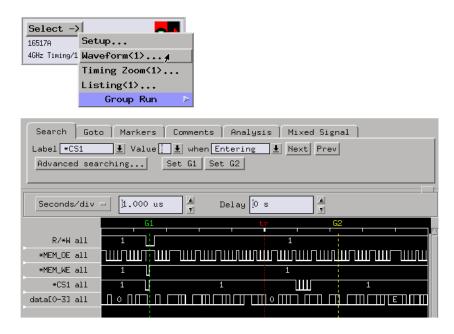

2. Assign pods if necessary.

Acquisition Depth 2M

Sample Period 3.0ns

Timing Zoom

<u>+</u>

3. Format labels for the signals or patterns of interest.

## **Capturing the Data**

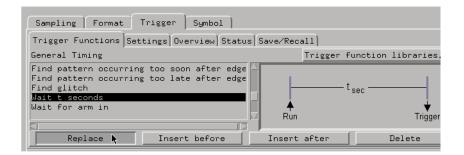

1. Use the "Find pattern absent for > duration" trigger function.

2. In the trigger definition, specify the pattern and the amount of time absent.

3. Select the Run button to start the measurement.

#### Displaying the Data

1. In the Waveform display (depending on the time between the edge/pattern and the trigger) you may be able to see the last time the edge/pattern occurred.

#### See Also

"Use trigger functions for easy measurement set up" on page 305

# To delay capture after a pattern

#### Possible uses:

- To hold off the trigger and look at control signals later than when the address bus pattern becomes invalid.

- To look for a receiver's response which is supposed to occur 3 milliseconds after a transmission.

# Probing the Target System

1. Configure a timing analysis machine.

2. Assign pods if necessary.

3. Format a label for the signals on which you will look for a stable pattern.

#### **Capturing the Data**

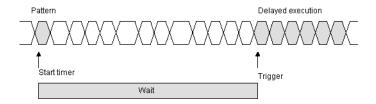

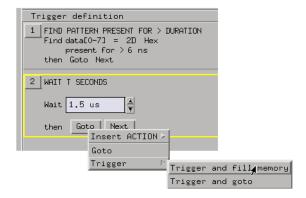

1. Build a two level trigger setup using the "Find pattern present for > duration" and "Wait t seconds" trigger functions.

2. In the trigger definition, specify the pattern and the amount of time present. Then, enter the amount of time to wait.

3. Select the Run button to start the measurement.

## **Displaying the Data**

1. In the Waveform display (depending on the time between the pattern and the trigger) you may be able to see the last time the pattern occurred.

#### See Also

"Use trigger functions for easy measurement set up" on page 305

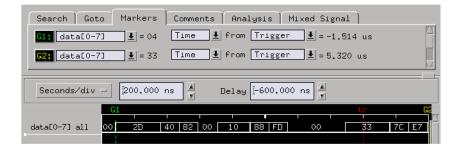

# To find an edge during a valid pattern

#### Possible uses:

- To capture a memory chip's select line at a given address.

- To view the timing of a write signal to a peripheral.

## Probing the Target System

$1. \ \ Configure \ a \ timing \ analysis \ machine.$

3. Format one label for the signals on which you will look for a pattern and another label for the signal on which you will look for the edge.

#### **Capturing the Data**

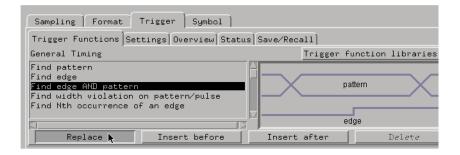

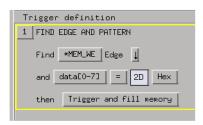

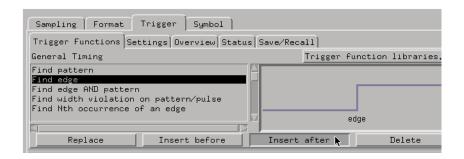

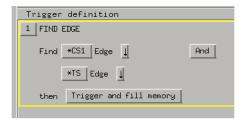

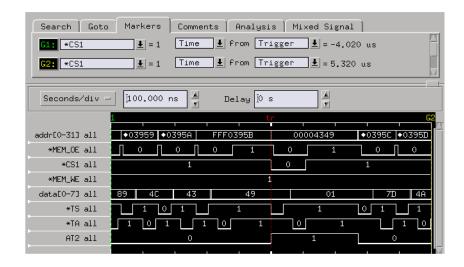

1. Use the "Find edge AND pattern" trigger function.

2. In the trigger definition, specify the edge and the pattern.

3. Select the Run button to start the measurement.

## **Displaying the Data**

1. When the analyzer triggers, use the Waveform display to show the edge in relation to the pattern.

If the analyzer never triggers, it could mean the pattern was never found or the edge never occurs when the pattern is valid.

#### See Also

"Use trigger functions for easy measurement set up" on page 305

"If the trigger doesn't occur as expected" on page 309

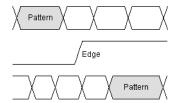

## To find a pattern, an edge, and another pattern

## Possible uses:

- To view a correct address bus, control signal, data bus sequence.

- To check whether a data packet was sent, a handshake signal followed, and an acknowledgement was returned.

## Probing the Target System

1. Configure a timing analysis machine.

3. Format labels for the signals on which you will look for the edge and patterns.

#### **Capturing the Data**

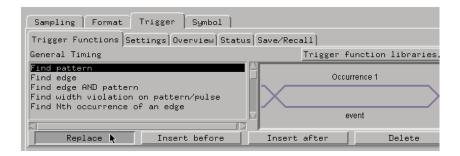

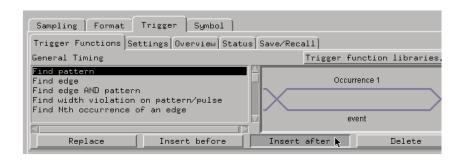

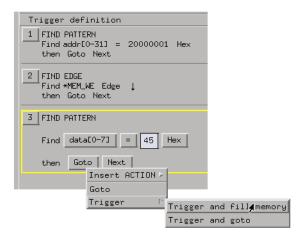

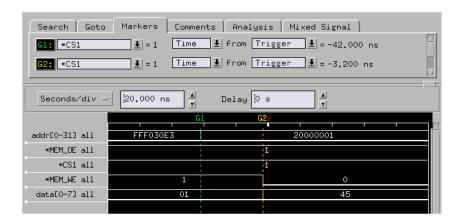

1. Build a three level trigger setup using the "Find pattern", "Find edge", and "Find pattern" trigger functions.

2. In the trigger definition, specify the first pattern and the amount of time present. Then, specify the edge. Finally, specify the second pattern and the amount of time present.

3. Select the Run button to start the measurement.

#### **Displaying the Data**

1. When the analyzer triggers, use the Waveform display to show the proper sequence was captured.

If the analyzer never triggers, the proper sequence does not occur. Depending on the level that was reached in the sequence above, you will need to set up a different trigger to see what actually occurs.

"Use trigger functions for easy measurement set up" on page 305

"If the trigger doesn't occur as expected" on page 309

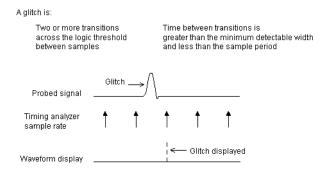

## To find signal glitches

#### Possible uses:

• To look for pulses more narrow than the minimum pulse width.

#### See Also

#### **Hardware Turn-On**

#### Probing the Target System

- 1. Connect the logic analyzer probes to the signals on which you will look for glitches.

- 2. Configure a timing analysis machine.

The sample period will specify what is interpreted as a glitch.

If the logic analyzer has a special acquisition mode for capturing glitches, select that mode.

#### NOTE:

You must select the glitch capture mode in order to see the glitch symbol in the Waveform display.

4. Format labels for the signals of interest.

#### **Capturing the Data**

You can trigger on anything, on any glitch, or on a particular glitch.

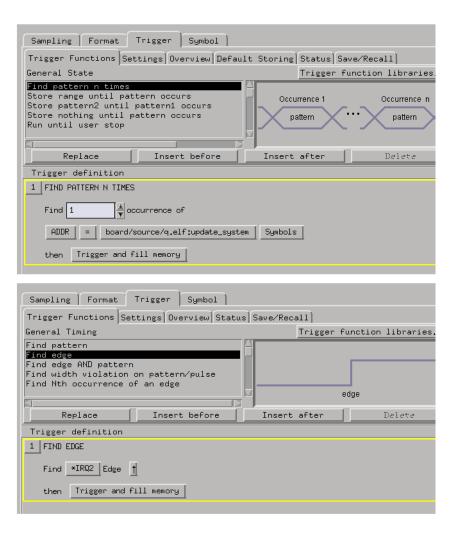

1. Use the "Find edge" trigger function.

## **Hardware Turn-On**

2. In the trigger definition, specify the signal on which you will look for glitches.

3. Select the Run button to start the measurement.

## **Displaying the Data**

1. Use the Waveform display to show the captured glitches.

2. Use the TimingZoom display to get a better picture of the glitch.

#### See Also

"To arm an oscilloscope when the analyzer triggers" on page 277

# Measuring Conformance to Specifications

- "To measure conformance to specs (with the Compare tool)" on page 51

- "To find setup and hold violations" on page 56

- "To trigger if a pattern doesn't follow an edge" on page 59

- "To verify pulse widths" on page 63

- $\bullet\,\,\,$  "To trigger on a violation of an edge sequence" on page  $67\,\,$

- "To trigger when two edges are asserted simultaneously" on page  $71\,$

- "To generate pattern stimulus on devices" on page 75

- $\bullet\,\,\,$  "To analyze jitter or time dispersion (with SPA)" on page 81

- "To analyze bus stability (with SPA)" on page 88

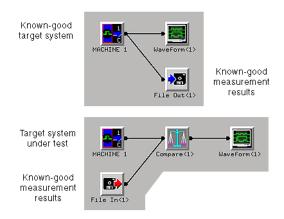

# To measure conformance to specs (with the Compare tool)

## Possible uses:

- To measure specifications conformance against known-good circuitry.

- To measure specifications conformance under component stress conditions.

## Probing the Target System

1. Configure a timing or state machine.

3. Format labels for the signals of interest.

#### **Capturing the Data**

1. Set up a trigger specification.

- 2. Select the Run button to start the measurement.

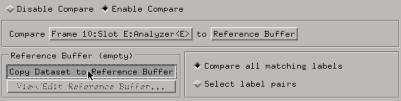

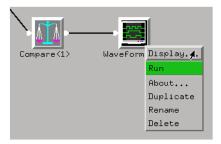

- 3. In the Workspace window, add the Compare tool to your analyzer configuration and copy the known-good dataset to the Compare tool's *reference buffer*.

- 4. If you want to turn OFF the analyzer and probe a different target system, save the Compare tool configuration. This will save the contents of the Reference Buffer to the logic analyzer's disk.

- 5. Probe a different target system or add the component stress conditions.

- 6. If you saved a Compare tool configuration, load it.

- 7. Select the Run button to repeat the measurement.

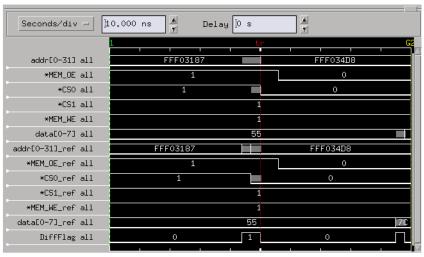

## **Displaying the Data**

1. In the display window, differences in the measurement results will be highlighted with gray.

Note that a *difference flag* label is generated so you can search for differences.

See Also

The Compare tool online help (see the Compare Tool help volume) for

more information.

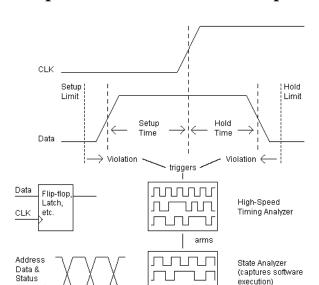

# To find setup and hold violations

#### Possible uses:

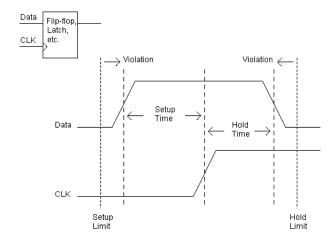

Verifying that design timing meets setup and hold specifications of flipflops, latches, and other memory element circuitry.

## Requirements:

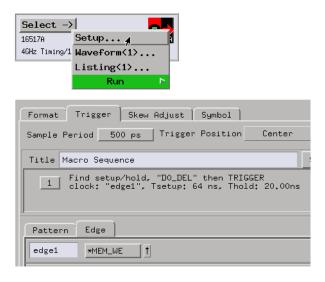

• The Agilent Technologies 16517A 4GHz Timing/1GHz State Logic Analyzer can look for setup and hold violations on multiple channels (for example, a data bus).

## Probing the Target System

1. Configure a timing analysis machine.

2. Format labels for the signals of interest.

## **Capturing the Data**

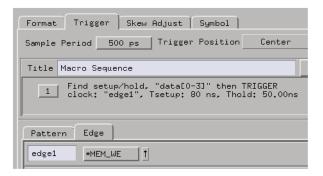

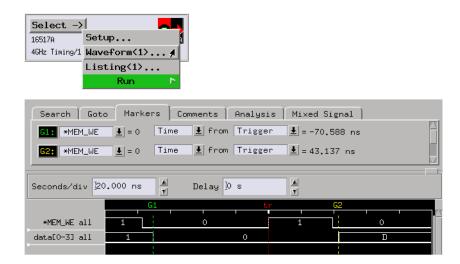

1. In the Trigger window, replace level 1 of the trigger specification with the "Find setup or hold violation" macro. In the macro dialog, select the label, edge, setup time limit, and hold time limit.

#### **Hardware Turn-On**

2. Set up the edge resource.

3. Select the Run button to start the measurement.

#### **Displaying the Data**

If the analyzer triggers, a setup or hold violation occurs. Open the Waveform display and use the global markers to see the actual setup or hold time.

#### See Also

To see how setup and hold violations affect software execution, (see "To capture SW execution on a setup or hold violation" on page 289).

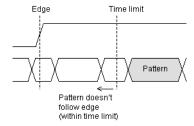

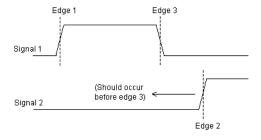

## To trigger if a pattern doesn't follow an edge

#### Possible uses:

• To measure interrupt response time.

• To trigger when expected data does not appear on the data bus from a remote device when requested.

### Probing the Target System

1. Configure a timing analysis machine.

3. Format one label for the signals on which you will look for a pattern and another label for the signal on which you will look for the edge.

## **Capturing the Data**

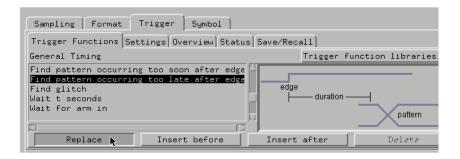

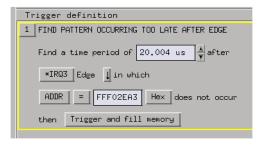

1. Use the "Find pattern occurring too late after edge" trigger function.

2. In the trigger definition, enter the time period and specify the edge and the pattern.

3. Select the Run button to start the measurement.

#### **Displaying the Data**

1. When the analyzer triggers, use the Waveform display to show that the pattern didn't occur after the edge. Use the Search dialog to find the edge and the pattern.

If the analyzer never triggers, the pattern always occurs after the edge within the time specified.

#### See Also

"Use trigger functions for easy measurement set up" on page 305

"If the trigger doesn't occur as expected" on page 309

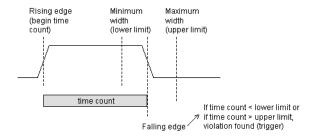

## To verify pulse widths

#### Possible uses:

- To test minimum and maximum pulse limits.

- To verify that all pulses controlling a mechanical device fall within specifications.

## Probing the Target System

1. Configure a timing analysis machine.

3. Format a label for the signal whose pulses you will be looking at.

## **Capturing the Data**

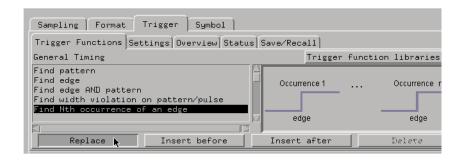

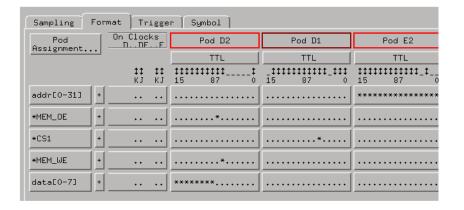

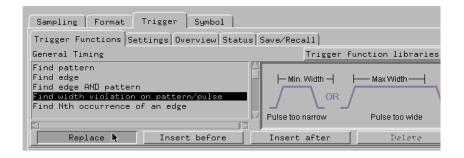

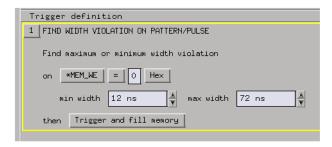

1. Use the "Find width violation on pattern/pulse" trigger function.

2. In the trigger definition, specify the pattern and enter the minimum and maximum widths.

3. Select the Run button to start the measurement.

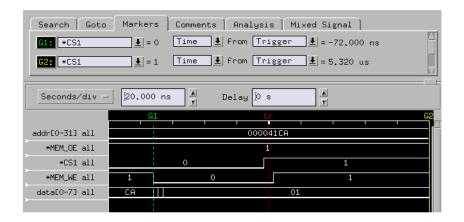

#### **Displaying the Data**

1. When the analyzer triggers, use the Waveform display to show that the trailing edge of the pulse didn't occur within the defined interval.

If the analyzer never triggers, the falling edge occurs within the defined interval.

#### See Also

"Use trigger functions for easy measurement set up" on page 305

"If the trigger doesn't occur as expected" on page 309

# To trigger on a violation of an edge sequence

#### Possible uses:

- To detect a handshake violation.

- To trigger on incorrect control signal generation from a Programmable Logic Device (PLD).

## Probing the Target System

1. Configure a timing analysis machine.

3. Format labels for the signals whose edges you will be looking at.

## **Capturing the Data**

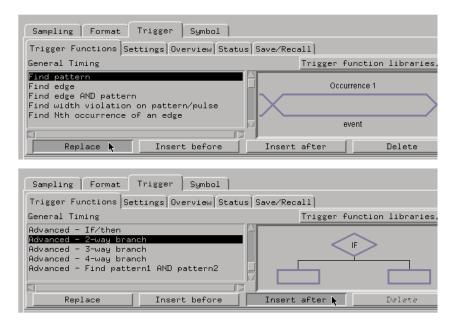

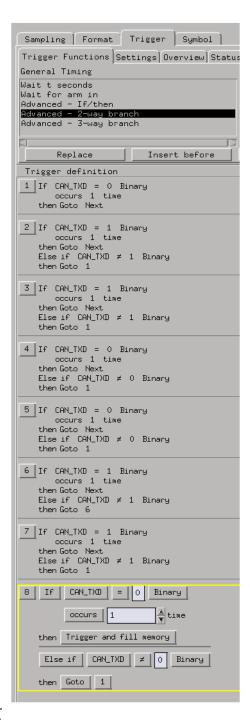

1. Build a two level trigger setup using the "Find pattern" and "Advanced 2-way branch" trigger functions. The pattern will identify when the edge sequence is about to occur and the 2-way branch will check for the sequence of edges.

2. In the trigger definition, specify the pattern and the edges. If edges occur in the wrong sequence, trigger the logic analyzer; otherwise, go back and look for the next occurrence of the edges.

3. Select the Run button to start the measurement.

#### Displaying the Data

1. When the analyzer triggers, use the Waveform display to show the edge sequence violation.

If the analyzer never triggers, the edges occur in the proper sequence.

See Also

"If the trigger doesn't occur as expected" on page 309

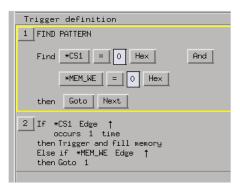

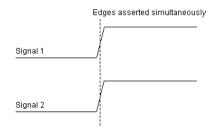

# To trigger when two edges are asserted simultaneously

#### Possible uses:

- To detect bus contention.

- To view system activity when two entities are trying to seize a digital communications channel at once.

# Probing the Target System

1. Configure a timing analysis machine.

3. Format labels for the signals whose edges you will be looking at.

### **Capturing the Data**

1. Use the "Find edge" trigger function.

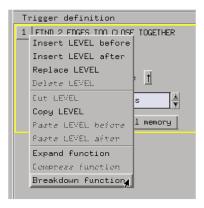

2. In the trigger definition, select the button after Find, and choose the "Insert LABEL after" item. Specify the two edges.

3. Select the Run button to start the measurement.

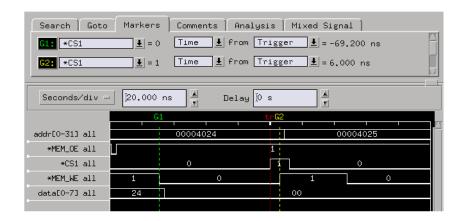

## **Displaying the Data**

1. When the analyzer triggers, use the Waveform display to show the two edges that occur at the same time.

If the analyzer never triggers, the two edges don't occur within the same sample period.

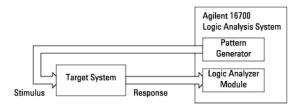

### To generate pattern stimulus on devices

## Requirements:

• This measurement requires a pattern generator module (Agilent Technologies 16522A).

#### Possible uses:

- $\bullet \quad$  To simulate digital circuitry that isn't available.

- To generate signals for functionally testing prototype hardware.

### Connecting Pattern Generator Outputs to the Target System

1. Connect the pattern generator lines to your target system using the appropriate TTL, CMOS, or ECL data or clock pods (see the pattern generator documentation (see the *Agilent Technologies 16522A 200M Vectors/s Pattern Generator* help volume) for more information).

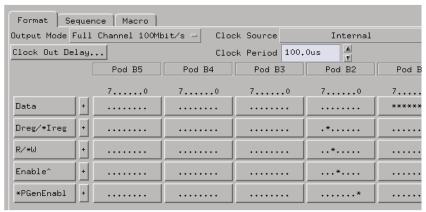

### Configuring the Pattern Generator & Labeling Outputs

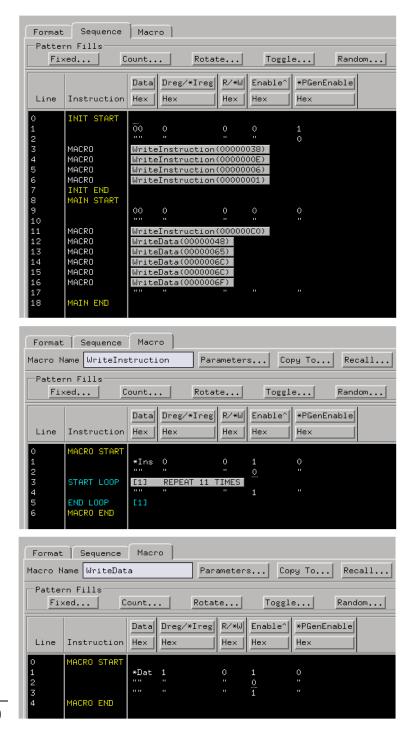

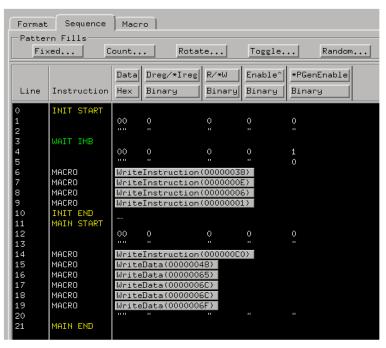

1. In the Format tab, select the output mode and the clock source, and label the output signals.

### Building the Test Vectors

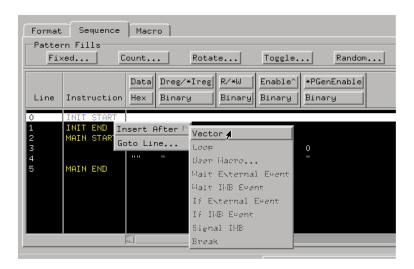

1. In the Sequence tab, insert vectors. Select data values, and enter the new values. A double-quote character means the same value as above.

During a repetitive run, the vectors in the INIT section are only executed once.

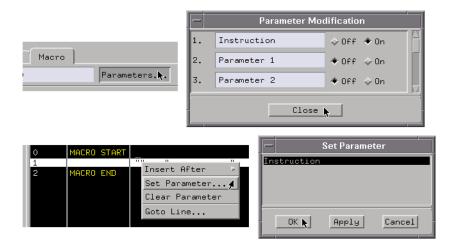

You can use macros to insert vectors that need to be repeated.

You can pass parameters to macros.

### Running the Pattern Generator

1. When you've finished building the test vectors, select the Run button to cause the pattern generator to output the vectors.

#### **Hardware Turn-On**

#### See Also

"To simulate particular interrupt sequences" on page 191

"To generate patterns when a source line executes" on page 262

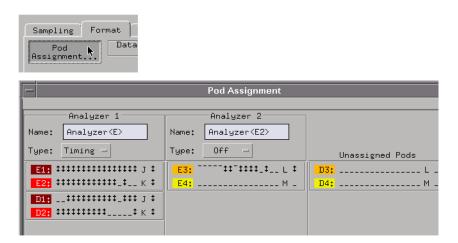

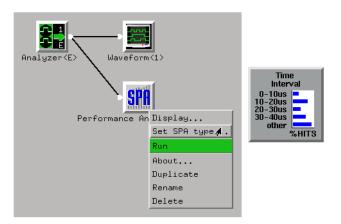

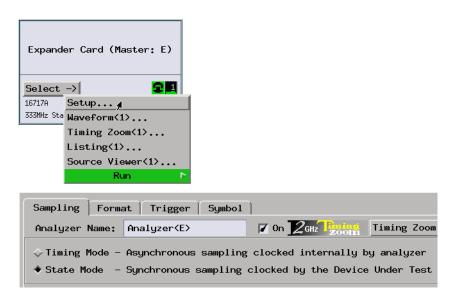

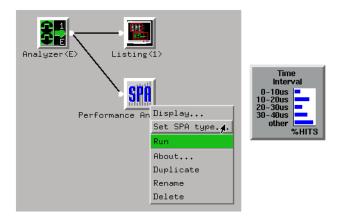

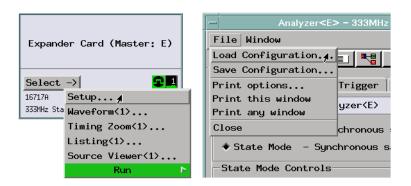

# To analyze jitter or time dispersion (with SPA)

### Requirements:

• This measurement requires the system performance analyzer (SPA) tool set.

#### Possible uses:

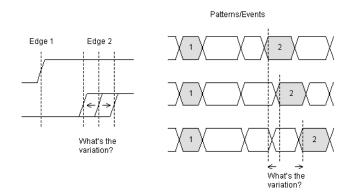

- To measure the jitter between two edges.

- To measure the variation between two bus states.

- To measure setup and hold times.

### Probing the Target System

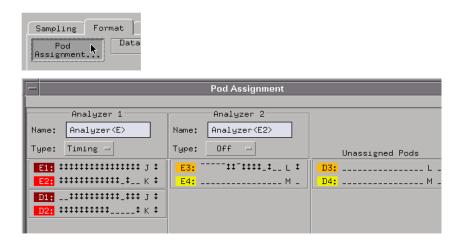

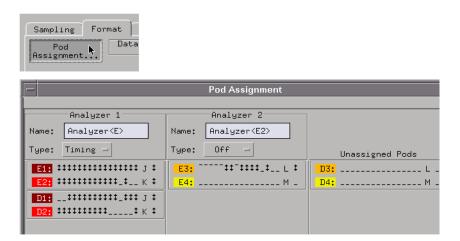

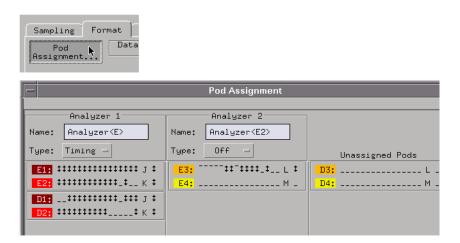

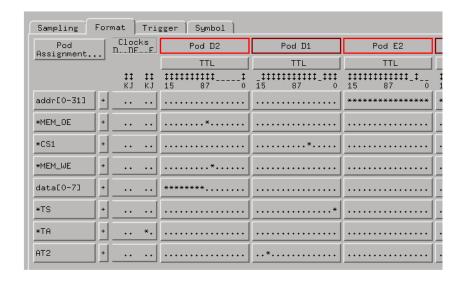

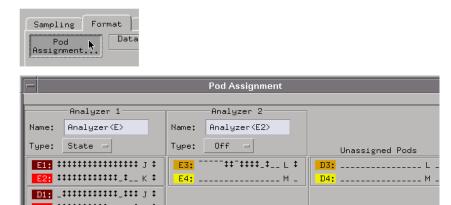

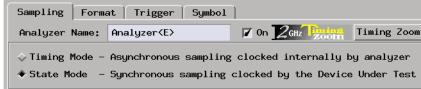

- 1. Probe the signals of interest.

- 2. Configure a timing or state analyzer, depending on whether you want to look at signal edges, patterns, or events.

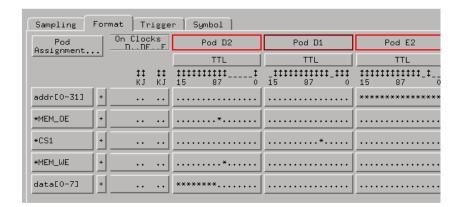

3. Assign pods if necessary.

Unassigned Pods

Timing -

4. Label the logic analyzer channels. (If you're using an analysis probe, you can configure the analyzer and set up labels by loading the included configuration files.)

Type:

E3:

#### **Capturing the Data**

1. Set up a trigger specification to capture the signal edges, patterns, or events you're interested in.

- 2. Select the Run button to start the measurement.

- 3. Display the captured waveforms.

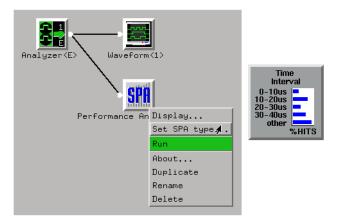

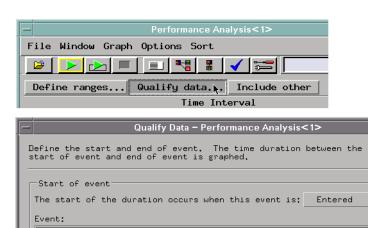

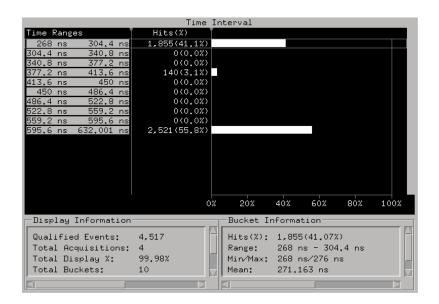

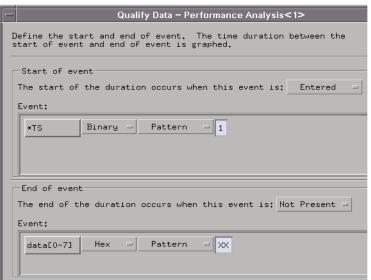

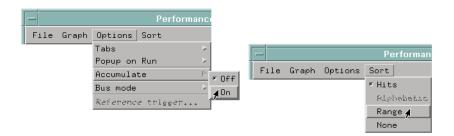

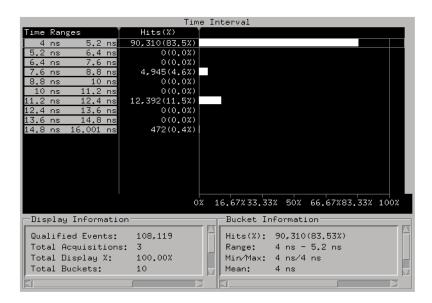

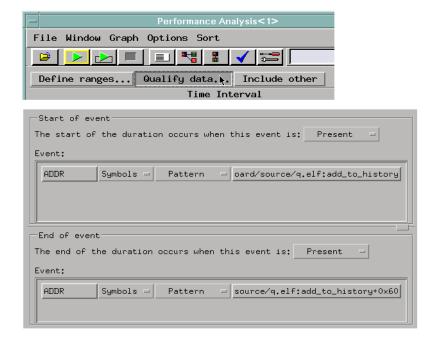

## **Displaying the Data**

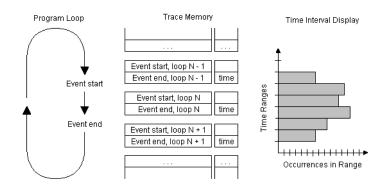

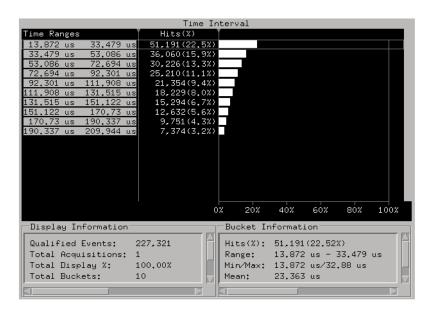

1. Use the system performance analyzer's Time Interval display to view the captured data.

2. Define the start and end of the event whose time variations you wish to measure.

Pattern

The end of the duration occurs when this event is: Entered

Pattern

- 0

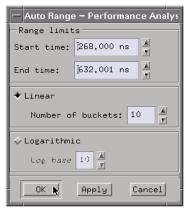

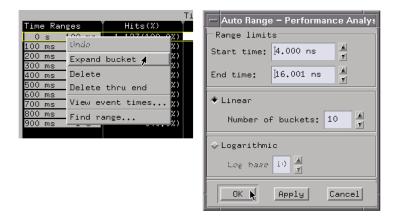

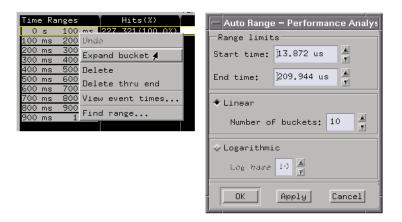

3. Define *buckets* for expected time ranges.

Binary -

Binary =

\*CS1

Event:

End of event

4. Set the appropriate data gathering and display options.

Use Accumulate Mode to analyze the behavior of your system over a long period of time (and, perhaps, run the measurement repetitively).

5. Run the measurement (and, perhaps, stop the measurement if it's running repetitively) and view the results.

Statistics such as the maximum time, minimum time, standard deviation, and mean help you document system behavior.

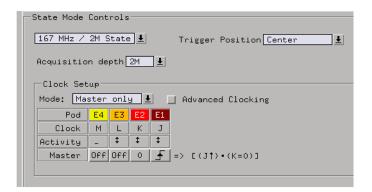

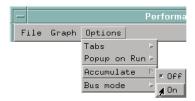

# To analyze bus stability (with SPA)

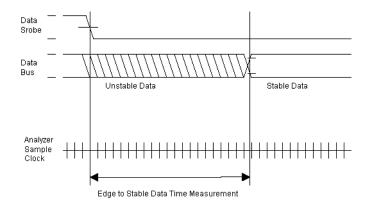

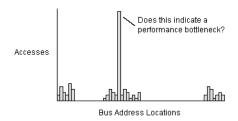

The stability of a bus is defined by two or more consecutive acquisitions of the same data value on the bus.

For example, if you analyze a microprocessor's access to a RAM, you want to be sure that the data is stable when it is strobed.

In this context, the system performance analyzer helps you characterize areas of stability or instability for this bus.

## Requirements:

• This measurement requires the system performance analyzer (SPA) tool set.

#### Possible uses:

- To measure the correlation between a signal (such as a strobe or an edge) and the presence of valid, stable information on a bus (or a label with one or more channels).

- To search on the entry or exit of a stable or unstable bus condition.

- To focus on bus transactions.

- To search for stability within a defined time range or outside a defined time range.

## Probing the Target System

1. Probe the bus and strobe signals of interest.

2. Configure a timing analyzer.

3. Assign pods if necessary.

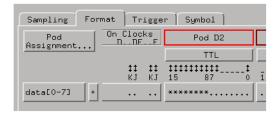

Sample Period 3.0ns

4. Label the logic analyzer channels.

## **Capturing the Data**

1. Set up a trigger specification to capture the strobe signal edge and the bus signals.

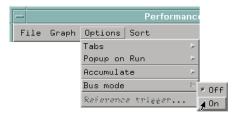

### **Displaying the Data**

1. Use the system performance analyzer's Time Interval display to view the captured data.

2. Define the start of the event as the data strobe signal going active, and define the end of event as the bus being stable (that is, a "don't care" pattern *Not Present*).

3. Turn ON the system performance analyzer's bus mode.

4. Define buckets for expected time ranges.

5. Set the appropriate data gathering and display options.

Use Accumulate Mode to analyze the behavior of your system over a long period of time (and, perhaps, run the measurement repetitively).

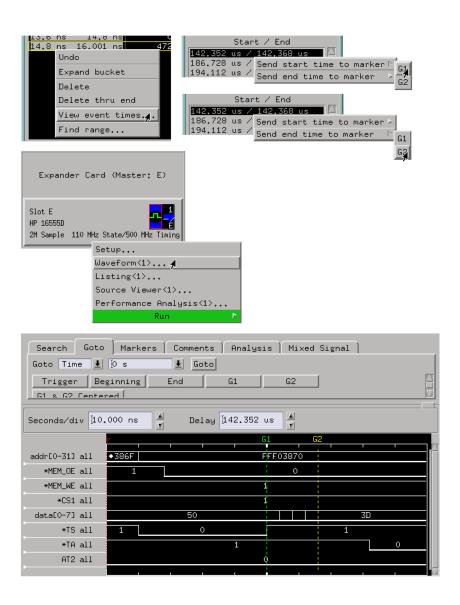

6. Run the measurement (and, perhaps, stop the measurement if it's running repetitively) and view the results.

You can use recorded event times to view an event in the Waveform display.

See Also

Bus Mode Search Criteria (see the *System Performance Analyzer* help volume) in the system performance analyzer help volume.

# Looking at State Events

- "To trigger on the Nth occurrence of an event" on page 96

- "To store N samples of an event" on page 100

- "To trigger on a sequence of events" on page 105

- "To trigger when a program loop exits" on page 111

- "To find events that are too close or too far" on page 116

- "To count occurrences of an event between two events" on page 120

- "To trigger on a function call sequence" on page 125

- "To analyze bus occupation & bandwidth (with SPA)" on page 131

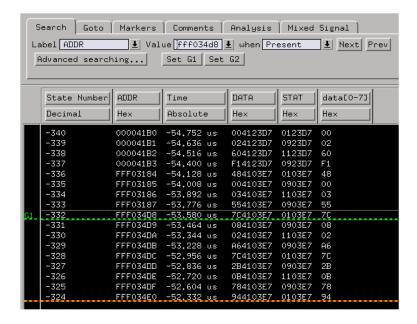

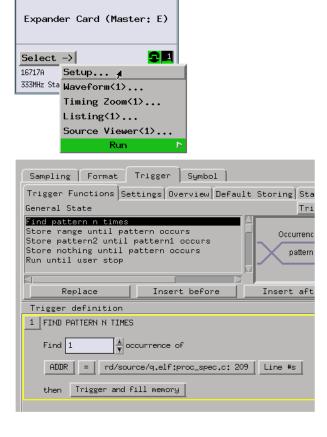

### To trigger on the Nth occurrence of an event

#### Possible uses:

- To find the 50th occurrence of a digital signal processing (DSP) subroutine.

- To trigger on the 3rd write to a specific memory address.

### Probing the Target System

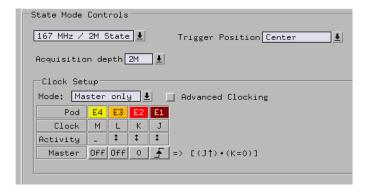

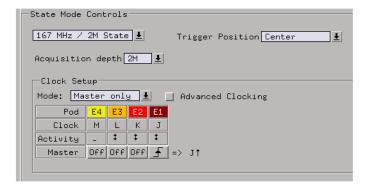

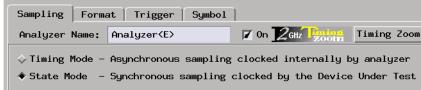

1. Configure a state analysis machine.

2. Select the state analyzer's clock input.

3. Format labels for the signals on which you will look for the event.

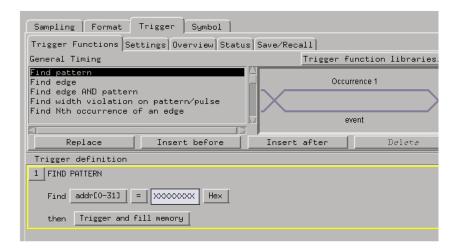

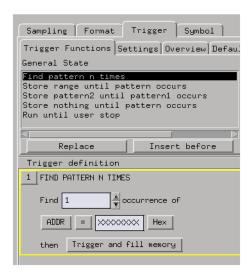

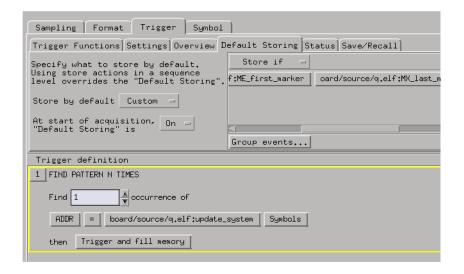

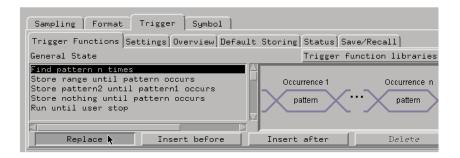

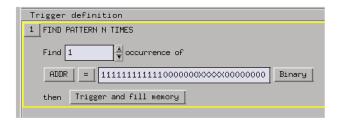

#### **Capturing the Data**

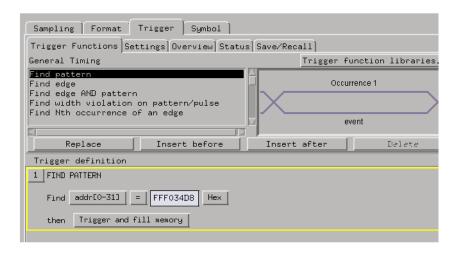

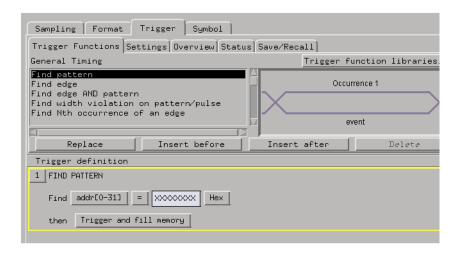

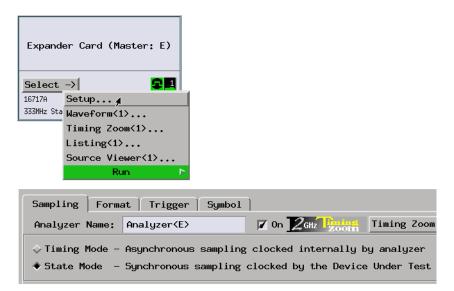

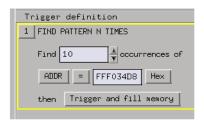

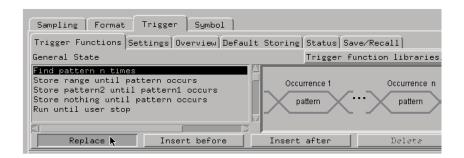

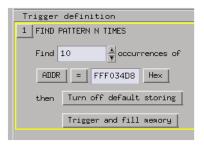

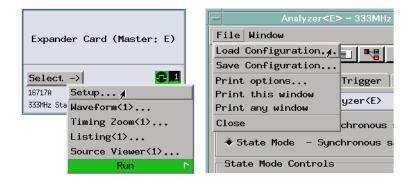

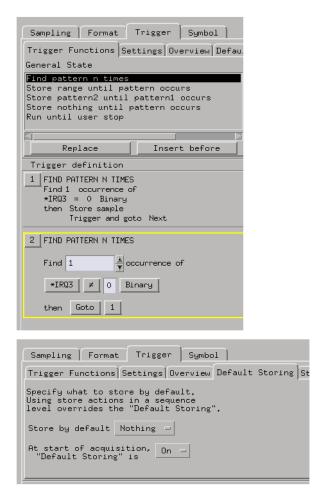

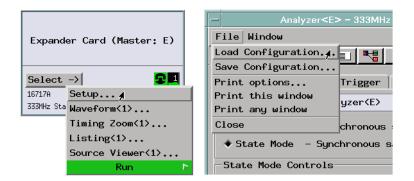

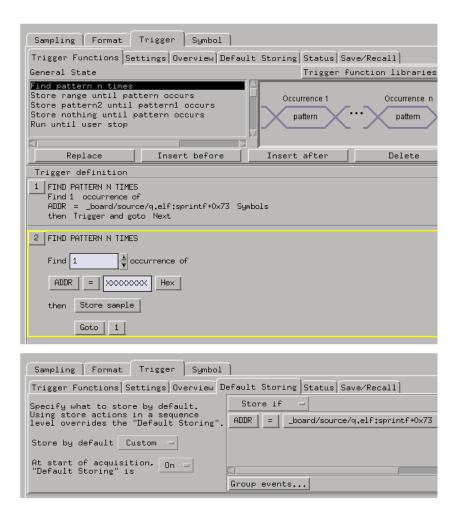

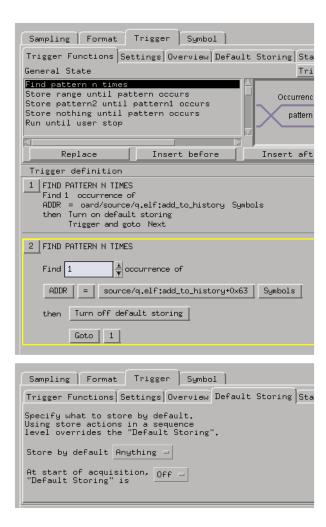

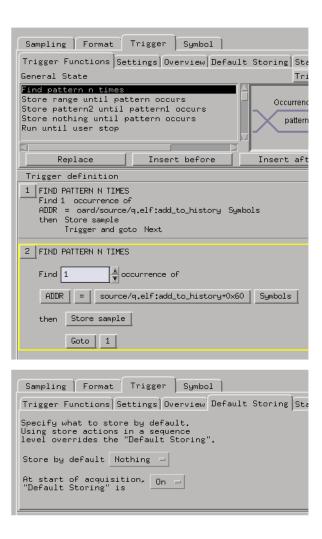

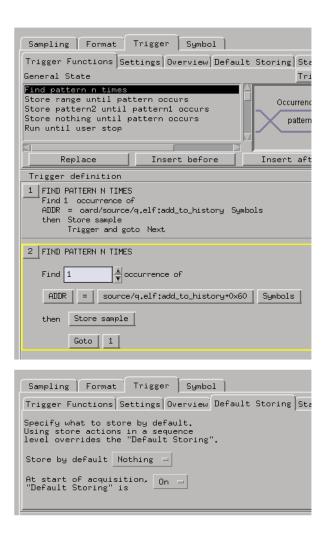

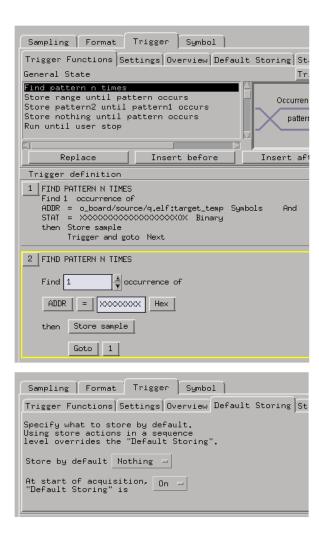

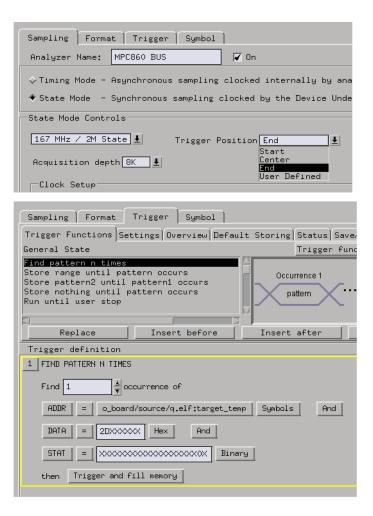

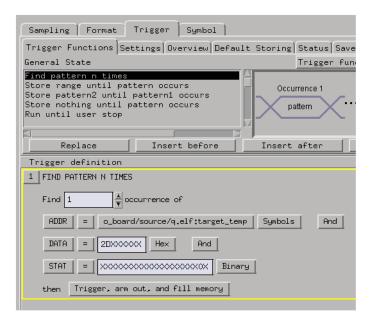

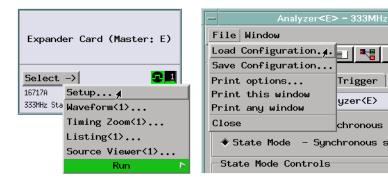

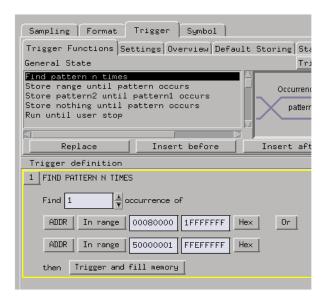

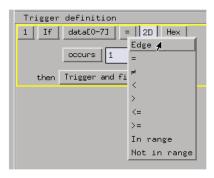

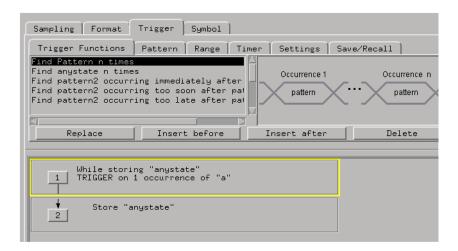

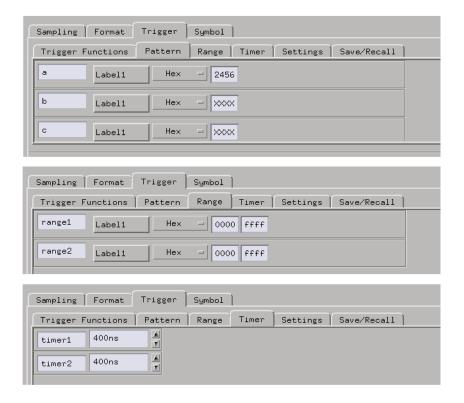

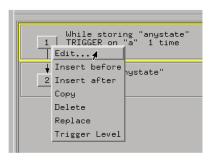

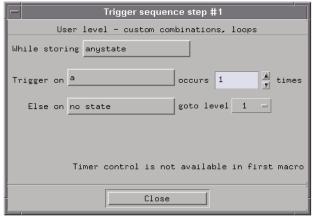

1. In the Trigger tab, use the "Find pattern n times" trigger function.

2. In the trigger definition, enter the number of occurrences and specify the pattern.

Use the default storage qualifier that is initially on and stores all states.

3. Select the Run button to start the measurement.

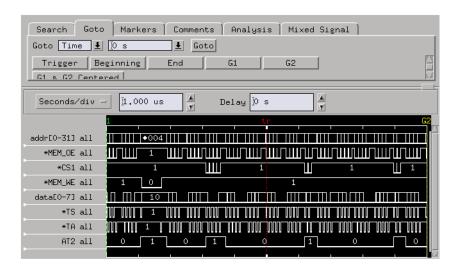

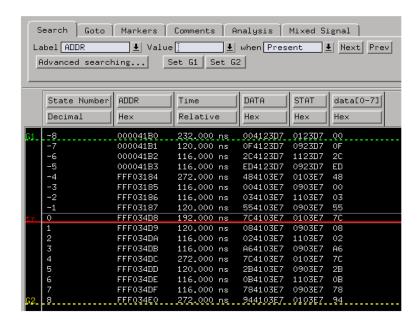

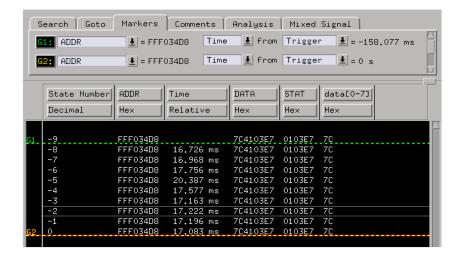

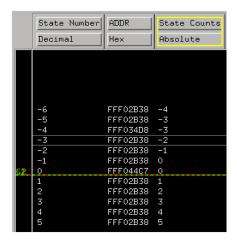

#### **Displaying the Data**

1. When the analyzer triggers, use the Listing display to show that the event occurred the number of times you specified.

If the analyzer never triggers, the event does not occur the number of times specified. You can stop the measurement and look at the Listing display to see how many times the event did occur.

#### See Also

<sup>&</sup>quot;Use trigger functions for easy measurement set up" on page 305

<sup>&</sup>quot;If the trigger doesn't occur as expected" on page 309

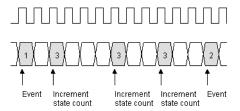

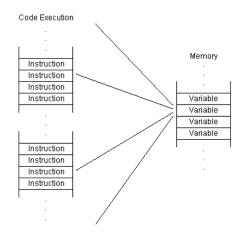

# To store N samples of an event

Logic Analyzer Acquisition

Sampling

Circuitry

Data Recognition

& Filtering

While storing

(only) event,

trigger on Nth

occurrence

of event

Qualified data

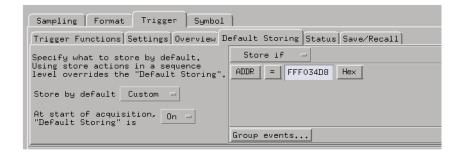

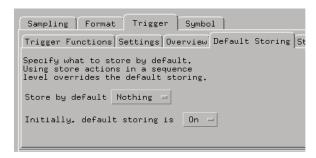

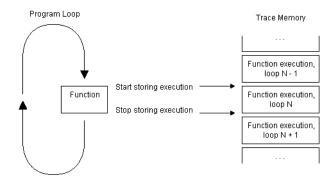

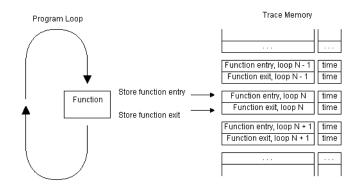

You can limit the data that is stored in trace memory at each trace sequence level or by specifying whether trace level branches are stored.

### Possible uses:

- To view the first 200 reads and writes to a FIFO.

- To look at 75 pushes onto the stack.

## Probing the Target System

1. Configure a state analysis machine.

2. Select the state analyzer's clock input.

3. Assign pods if necessary.

4. Format labels for the signals on which you will look for the event.

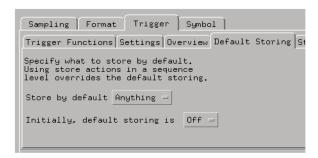

### **Capturing the Data**

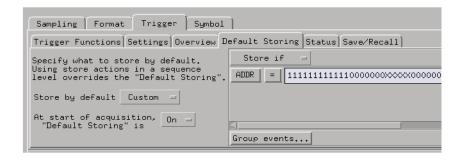

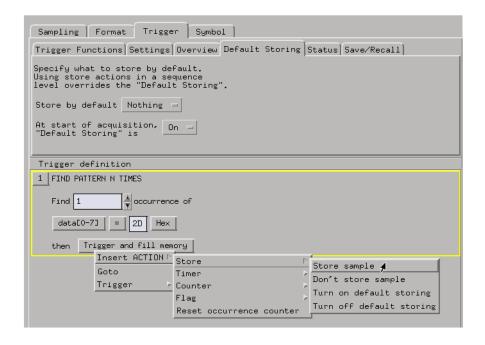

1. In the Trigger tab, use the "Find pattern n times" trigger function.

2. In the trigger definition, specify the event and the number of samples you want to store. Also, insert an action to turn off default storing after the number of events occur.

3. Set up the default storing to store only the event you're interested in.

- 4. Select the Run button to start the measurement.

- 5. Select the Stop button after the trigger occurs. (Because default

storing is turned off after the trigger, trace memory will not fill up.)

### **Displaying the Data**

1. When the analyzer triggers, use the Listing display to show that N event occurrences are stored.

If the analyzer never triggers, the event does not occur N times. You can stop the measurement and look at the Listing display to see how many times the event did occur.

#### See Also

"If the trigger doesn't occur as expected" on page 309

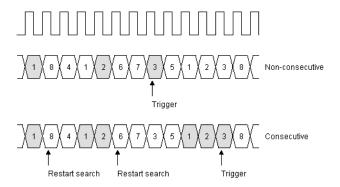

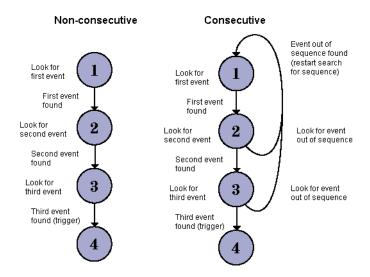

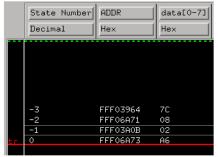

# To trigger on a sequence of events

#### Possible uses:

- To trigger on the occurrence of a calculation subroutine after two

initialization subroutines have executed (non-consecutive sequence of

events).

- To trigger on the access to an I/O port *after* its two I/O registers have been set (non-consecutive sequence of events).

- To trigger on the occurrence of a subroutine only when it has been called from a specific branch of the main program (consecutive sequence of events).

- To look for data writes to 4 consecutive memory locations with no reads inbetween (consecutive sequence of events).

## Probing the Target System

1. Configure a state analysis machine.

2. Select the state analyzer's clock input.

3. Assign pods if necessary.

4. Format labels for the signals on which you will look for the event.

#### **Capturing the Data**

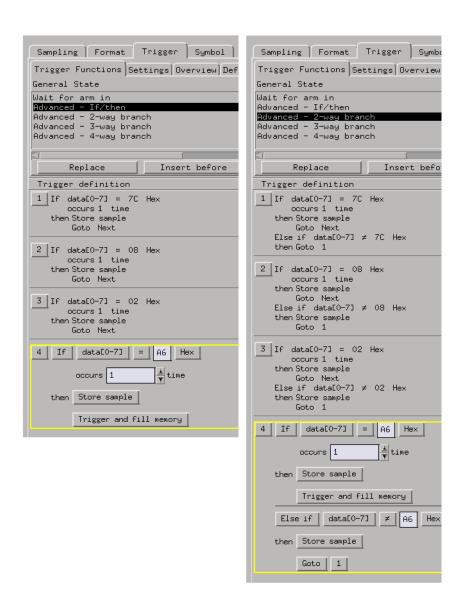

1. To look for a sequence of non-consecutive events, set up a trigger sequence where level 1 looks for the first event; when it's found, level 2 looks for the second event, and so on. The second to last sequence level looks for the last event and triggers the analyzer when it's found.

To look for a sequence of consecutive events, set up a trigger sequence where level 1 looks for the first event; when it's found, level 2 looks for the second event (which if found causes a branch to the next level) or a state that is not the second event or indicates an event out of sequence (which if found causes a branch back to the first level to restart the search).

Subsequent levels are the same as level 2. When the last event is found, the analyzer triggers, and the last sequence level is used to specify what is stored after the trigger.

Note that, when looking for a consecutive sequence of events, any event that disqualifies the sequence you're looking for can be used in the "else on" branches. For example, instead of looking for a particular sequence of states, you can look for a particular sequence of function calls.

To show the differences between these trigger definitions, nothing is

stored by default.

2. Select the Run button to start the measurement.

#### **Displaying the Data**

1. When the analyzer triggers, use the Listing display to show that the sequence of events occurred.

If the analyzer never triggers, at least one of the events in the sequence never occurs. You can stop the measurement and look at the Listing display to see which events in the sequence were captured.

#### See Also

"If the trigger doesn't occur as expected" on page 309

# To trigger when a program loop exits

```

Before_Loop

Loop_Start

In_Loop

...

Loop_End

After_Loop

```

#### Possible uses:

- To capture execution after a background monitor loop that runs until a control key is pressed.

- To verify that all stacks and registers are restored correctly before exiting a subroutine (that is, to look at code execution before exit).

#### Probing the Target System

1. Configure a state analysis machine.

2. Select the state analyzer's clock input.

3. Assign pods if necessary.

4. Format a label for the address bus signals on which you will look for loop start and loop end events. (If you are using an analysis probe, the included configuration files will format an ADDR label.)

#### **Capturing the Data**

1. Set up a trigger sequence where level 1 looks for the loop start event; when it's found, level 2 looks for the loop end event; when it's found level 3 looks for an event that isn't the loop start event (which if found triggers the analyzer) or the loop start event (which if found causes a branch back to level 2 where the loop end event is searched for).

To show only loop start and loop end events until the logic analyzer triggers, turn default storing off initially.

2. Select the Run button to start the measurement.

#### **Displaying the Data**

1. When the analyzer triggers, use the Listing display to show that the program loop exited.

If the analyzer never triggers, you can look at the run status message line to see which sequence levels are visited, and you can learn more about why the trigger never occurred.

See Also

"If the trigger doesn't occur as expected" on page 309

#### To find events that are too close or too far

You can measure time by using a timer or by counting states or the occurrences of an event.

#### Possible uses:

- To detect when a subroutine is exited prematurely from any number of exit points (events too close, not enough cycles between subroutine entry and exit).

- To find a protocol violation in sending control messages to a peripheral (where events that are too close violate the protocol).

- To trigger when secondary cache must be accessed between 2 consecutive memory reads, producing extra cycles (events too far, that is, there are too many cycles between consecutive memory reads).

- To detect when an interrupt routine is executing for an excessive number of cycles (events too far, that is, there are too many cycles between interrupt entry and exit).

- To examine code execution when circuitry issues a data request interrupt more than N times during the execution of a time-critical subroutine (events too far, that is, there are too many interrupts between subroutine entry and exit).

- To trigger if a loop is executed more than 10 times between 2 nonconsecutive routines (events too far, that is, there are too many loop executions between two routines).

#### Probing the Target System

1. Configure a state analysis machine.

2. Select the state analyzer's clock input.

3. Assign pods if necessary.

4. Format labels for the signals on which you will look for the events.

#### **Capturing the Data**

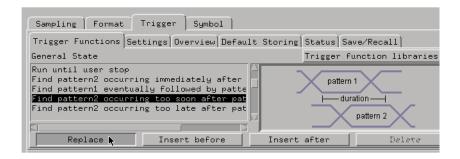

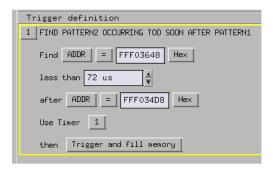

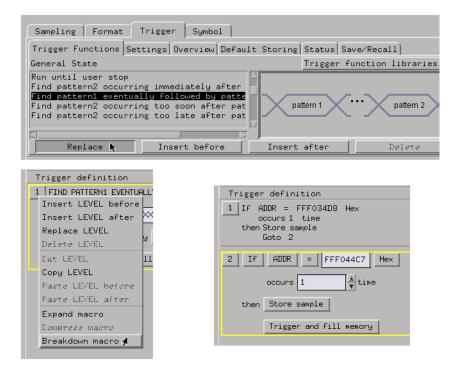

- 1. In the Trigger window, replace level 1 of the trigger specification with one of the following trigger functions:

- Find pattern2 occurring too soon after pattern1

- Find too few states between pattern1 and pattern2

- Find pattern2 occurring too late after pattern1

- Find too many states between pattern1 and pattern2

2. In the trigger definition, specify the patterns and enter the time limit.

3. Select the Run button to start the measurement.

### **Displaying the Data**

When the analyzer triggers, use the Listing display to show that fewer or more than N cycles, events, or some amount of time occurred between the two events.

#### See Also

"Use trigger functions for easy measurement set up" on page 305

"If the trigger doesn't occur as expected" on page 309

#### To count occurrences of an event between two events

#### Possible uses:

- To verify that a memory refresh routine is executing the number of times expected.

- To count the number of memory write cycles within a segment of code.

#### Probing the Target System

1. Configure a state analysis machine.

2. Select the state analyzer's clock input.

3. Assign pods if necessary.

4. Format labels for the signals on which you will look for the events.

#### **Capturing the Data**

1. Set up a trigger sequence where level 1 looks for the start event; when it's found, level 2 looks for the second event; when it's found trigger the analyzer.

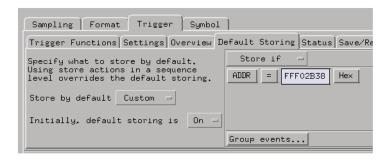

2. Store the start and end events and the event you want to count.

3. Change the count qualifier to count the event you are interested in.

4. Select the Run button to start the measurement.

# **Displaying the Data**

1. When the analyzer triggers, use the Listing display to show the start and end events. The difference in count values shows the number of times the count event occurred between the start and end events.

If the analyzer never triggers, the start or end events were never found. Look at the run status message to see which sequence levels are visited; this will tell you which event was not found.

#### See Also

"If the trigger doesn't occur as expected" on page 309

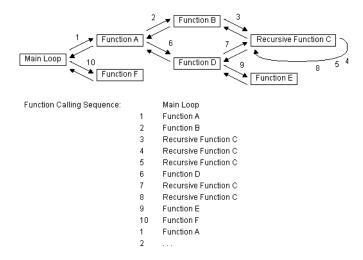

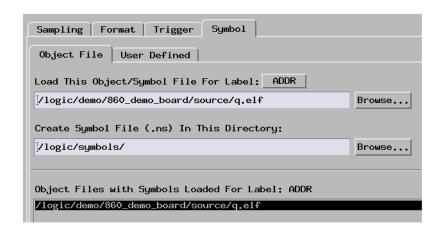

# To trigger on a function call sequence

#### Possible uses:

- To trigger when procedure 3 displays an error message, but only when it's called by procedure 2 and procedure 1 before that.

- To trigger on the 3rd nested occurrence of a recursive subroutine.

#### Probing the Target System

1. Configure a state analysis machine.

2. Select the state analyzer's clock input.

3. Assign pods if necessary.

4. Format labels for the signals on which you will look for the program flow events.

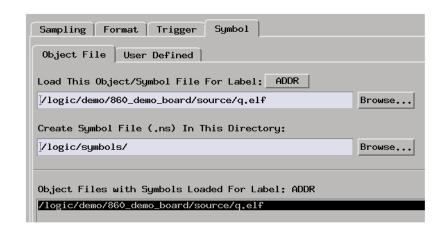

5. Load symbols from your program's object module file.

#### **Capturing the Data**

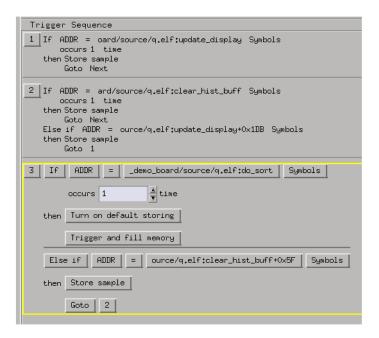

1. Set up a trigger sequence where level 1 looks for the procedure 1; when it's found, level 2 looks for procedure 2 or the end of procedure 1 (which if found will restart the search). Level 3 looks for procedure 3 (which if found will trigger the analyzer) or the end of procedure 2 (which if found will branch back to level 2).

2. In the trigger definition, specify the program flow events.

3. Set up default storing to be initially off.

4. Select the Run button to start the measurement.

## **Displaying the Data**

1. When the analyzer triggers, use the Listing display to show the particular sequence was captured.

If the analyzer never triggers, look at the run status message to see which sequence levels are visited; this will tell you which event was not found.

See Also

"If the trigger doesn't occur as expected" on page 309

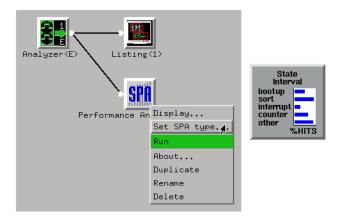

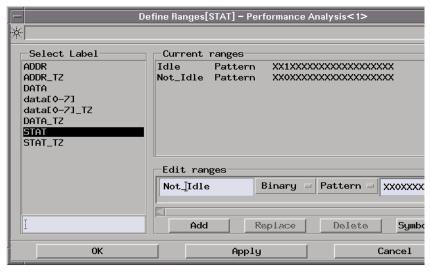

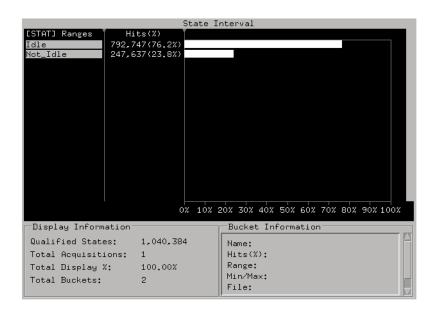

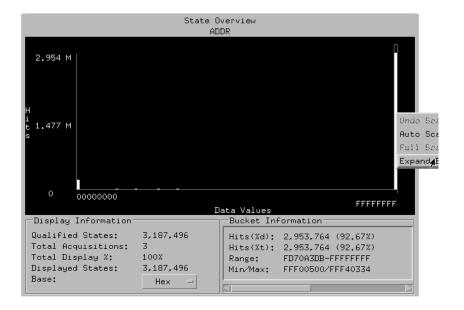

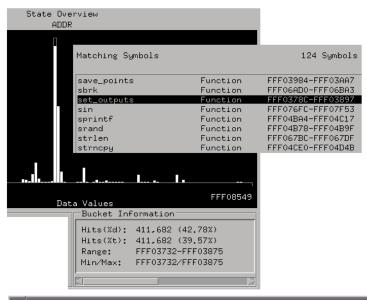

# To analyze bus occupation & bandwidth (with SPA)

Bus occupation and bandwidth measurements generally show the

amount of idle bus states among all bus states.

#### Requirements:

This measurement requires the system performance analyzer (SPA) tool set.

#### Possible uses:

- To show the share of the workload that each processor in a multipleprocessor system carries, or to determine if the system is balanced.

- To analyze headroom by examining the percentage of idle bus states.

- To analyze cache hits and misses.

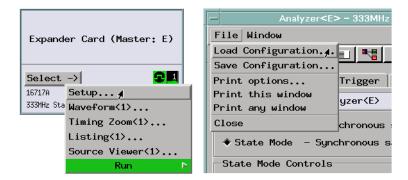

#### Probing the Target System

- 1. Probe the bus you wish to analyze.

- 2. Configure a state analysis machine.

3. Select the state analyzer's clock input.

4. Assign pods if necessary.

5. Label the logic analyzer signals. If you are using an analysis probe, you can configure and label signals with provided configuration files.

#### **Capturing the Data**

1. Set up a trigger specification to capture all activity on the bus.

2. Select the Run button to start the measurement.

#### **Displaying the Data**

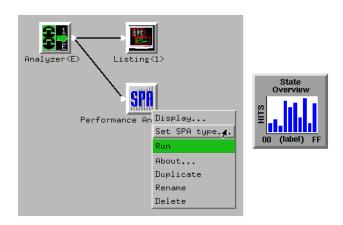

1. Use the System Performance Analyzer's State Interval display to view the measurement result.

2. Define a state range that corresponds to idle bus states.

#### **Hardware Turn-On**

There is no limit to the number of ranges that can be simultaneously defined and displayed. The ranges can be sorted alphabetically or by number of hits.

3. Run the measurement and view the results.

#### See Also

"To view bus activity" on page 174

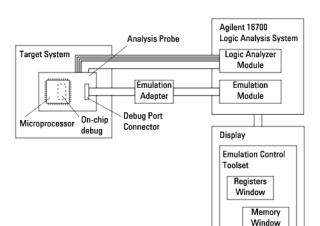

# Exercising the Microprocessor (with the Emulation Probe)

- "To initialize registers, access memory" on page 137

- "To use the emulation probe as a test tool" on page 140

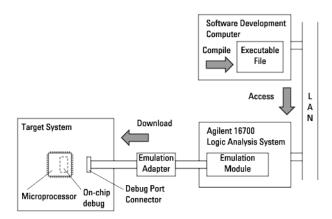

## To initialize registers, access memory

### Requirements:

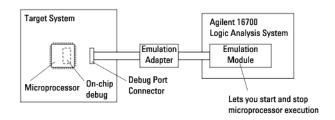

- Your target system microprocessor must have on-chip debug circuitry that an emulation probe can work with.

- The emulation probe connects to a debug port connector on the analysis probe or to a debug port connector designed into your target system.

- You need either the emulation control tool set in the Agilent Technologies 16700A/B-series logic analysis system or you need third-party debugger software to control the microprocessor debug interaction.

#### Possible uses:

- To test microprocessor access to target system memory or I/O.

- To modify the contents of microprocessor data or configuration registers.

- To prepare the target system for downloading code to RAM.

# Probing the Target System

- 1. Make sure the emulation probe (or emulation module and emulation adapter) has been connected to the target system.

- 2. Set up the emulation control tool set or third-party debugger connection to the emulation probe.

# **Control Software**

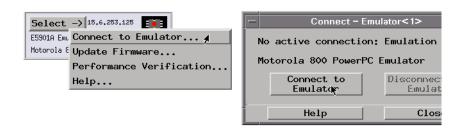

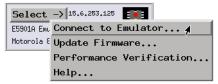

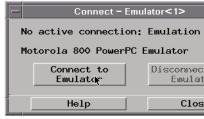

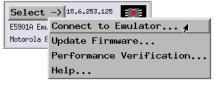

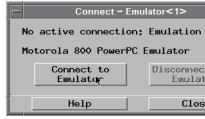

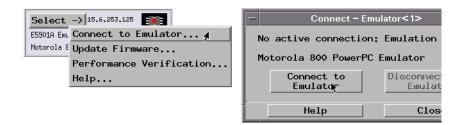

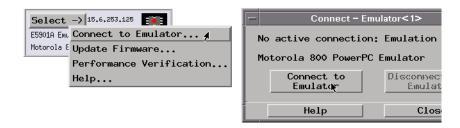

**Starting the Emulation** 1. Start an emulation module session.

If you have third-party debugger software (on a computer in the network), start that software, and connect it to the emulation probe.

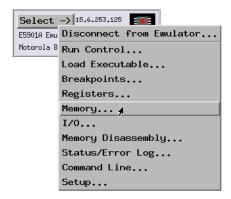

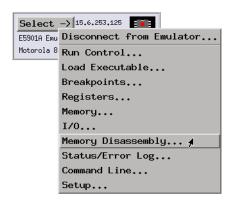

#### Accessing/Modifying Registers, Memory, or 1/0

1. In the emulation control tool set, open the Register, Memory, or I/O window, display the locations you're interested in, and modify particular locations.

If you are using a third-party debugger, perform these tasks using its interface.

#### See Also

"To download boot code" on page 144

"To use the emulation probe as a test tool" on page 140

# To use the emulation probe as a test tool

#### Requirements:

- Your target system microprocessor must have on-chip debug circuitry that an emulation probe can work with.

- The emulation probe connects to a debug port connector on the analysis probe or to a debug port connector designed into your target system.

- You need the emulation control tool set in the Agilent Technologies 16700A/B-series logic analysis system.

#### Possible uses:

- To automate a sequence of register, memory, or I/O access commands.

- To control the execution of the microprocessor as part of a system test.

### Probing the Target System

- 1. Make sure the emulation probe (or emulation module and emulation adapter) has been connected to the target system.

- 2. Set up the emulation control tool set connection to the emulation probe.

#### Creating/Editing the Command Script

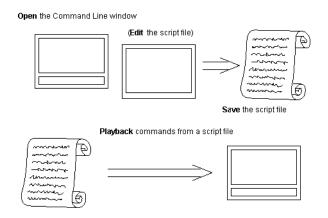

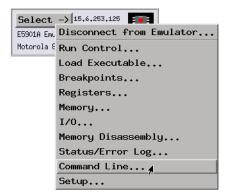

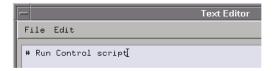

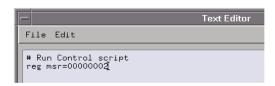

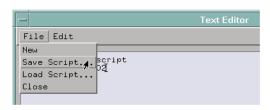

1. Access the Command Line window.

2. Select the Edit Script button.

3. Enter the comment line that identifies the file as a run control script.

4. Enter commands.

5. Save the script to a file.

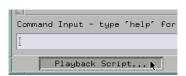

# Playing Back the Command Script

1. Select the Playback Script button and choose the run control script file.

See Also

"To initialize registers, access memory" on page 137

# Firmware Development

Testing Boot Code (with the Emulation Probe)

- "To download boot code" on page 144

- "To start or stop processor execution" on page 147

- "To stop processor execution using breakpoints" on page 149

- "To capture startup execution" on page 152

Making Driver Development Measurements

- "To trigger on an 8-bit serial pattern" on page 155

- "To view serial data in parallel" on page 160

- "To capture driver execution (& view HW and SW)" on page 165

- "To capture execution up to a failure or halt" on page 171

- "To view bus activity" on page 174

- "To capture simple program messages" on page 175

- "To trigger on packet data (with DataComm Analysis)" on page 177

Making Interrupt Service Routine Measurements

- "To capture interrupt frequency and type" on page 183

- "To measure interrupt latency and execution time" on page 186

- "To simulate particular interrupt sequences" on page 191

- "To view the occurrence rate of an event (with SPA)" on page 192

# Testing Boot Code (with the Emulation Probe)

- "To download boot code" on page 144

- "To start or stop processor execution" on page 147

- "To stop processor execution using breakpoints" on page 149

• "To capture startup execution" on page 152

#### To download boot code

#### Requirements:

- Your target system microprocessor must have on-chip debug circuitry that an emulation probe can work with.

- The emulation probe connects to a debug port connector on the analysis probe or to a debug port connector designed into your target system.

- You need the emulation control tool set in the Agilent Technologies 16700A/B-series logic analysis system.

#### Possible uses:

To move boot code into target system RAM for execution.

# Probing the Target System

- 1. Make sure the emulation probe (or emulation module and emulation adapter) has been connected to the target system.

- $2. \;\;$  Set up the emulation control tool set connection to the emulation probe.

# Downloading Boot Code

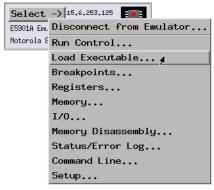

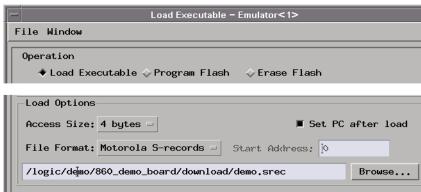

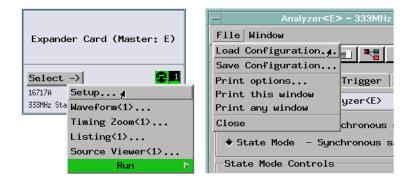

1. Access the Load Executable window.

- 2. Select the appropriate file format, options, and executable file name.

- 3. Select the Apply button to download the executable file.

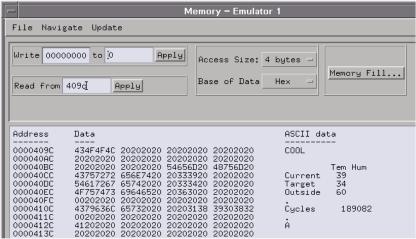

# Verifying the Download

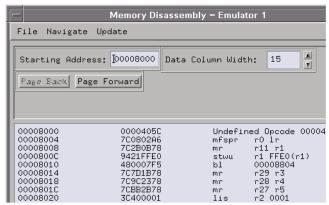

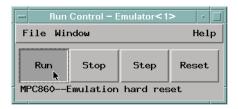

1. You can verify the download by looking at the memory locations in disassembled format.

#### See Also

"To initialize registers, access memory" on page 137 (if you need to initialize registers before code download)

# To start or stop processor execution

# Requirements:

- Your target system microprocessor must have on-chip debug circuitry that an emulation probe can work with.

- The emulation probe connects to a debug port connector on the analysis probe or to a debug port connector designed into your target system.

- You need either the emulation control tool set in the Agilent Technologies 16700A/B-series logic analysis system or you need third-party debugger software to control the microprocessor debug interaction.

#### Possible uses:

- To control the target system boot up sequence.

- To view the state of the microprocessor at particular points during program execution.

# **Probing the Target** System

- 1. Make sure the emulation probe (or emulation module and emulation adapter) has been connected to the target system.

- 2. Set up the emulation control tool set or third-party debugger connection to the emulation probe.

# **Control Software**

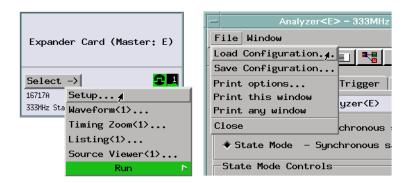

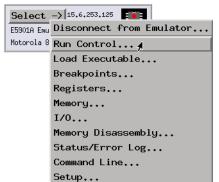

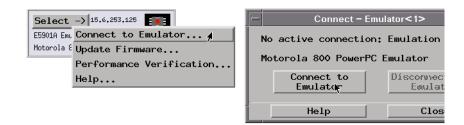

**Starting the Emulation** 1. If you have the emulation control tool set in your Agilent Technologies 16700A/B-series logic analysis system, drag the icon to the workspace, and connect to the emulation probe.

If you have third-party debugger software, start that software, and connect to the emulation probe.

# Execution

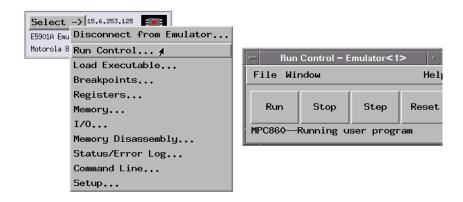

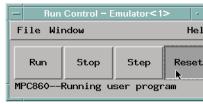

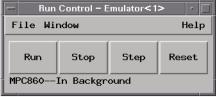

**Controlling Processor** 1. In the emulation control tool set, open the Run Control window, and select the Run or Stop buttons.

If you have a third-party debugger, perform these tasks using its interface.

#### See Also

"To stop processor execution using breakpoints" on page 149

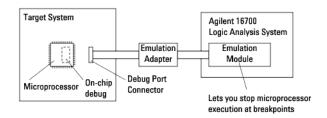

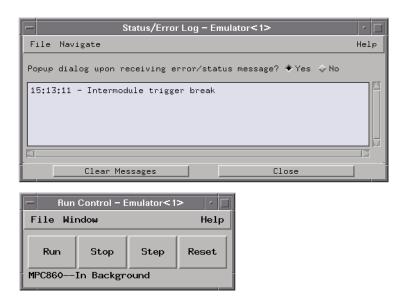

# To stop processor execution using breakpoints

# Requirements:

- Your target system microprocessor must have on-chip debug circuitry that an emulation probe can work with.

- The emulation probe connects to a debug port connector on the analysis probe or to a debug port connector designed into your target system.

- You need either the emulation control tool set in the Agilent Technologies 16700A/B-series logic analysis system or you need third-party debugger software to control the microprocessor debug interaction.

#### Possible uses:

- To stop microprocessor execution on a particular line of source code.

- To view the state of the microprocessor at particular points during program execution.

# **Probing the Target** System

- 1. Make sure the emulation probe (or emulation module and emulation adapter) has been connected to the target system.

- 2. Set up the emulation control tool set or third-party debugger connection to the emulation probe.

# **Control Software**

**Starting the Emulation** 1. If you have the emulation control tool set in your Agilent Technologies 16700A/B-series logic analysis system, drag the icon to the workspace, and connect to the emulation probe.

If you have third-party debugger software, start that software, and connect to the emulation probe.

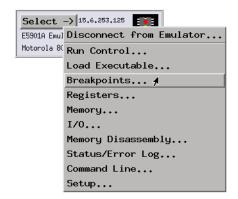

# **Setting Breakpoints**

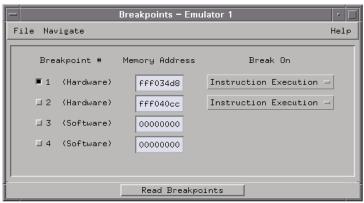

1. In the emulation control tool set, open the Breakpoints window, select a breakpoint to use, and enter the address at which microprocessor execution should stop.

Hardware breakpoints can be used for addresses in target system ROM.

Software breakpoints replace existing code with a breakpoint instruction, so they only work for addresses in target system RAM.

If you have a third-party debugger, perform these tasks using its interface.

See Also

"To start or stop processor execution" on page 147

# To capture startup execution

#### Possible uses:

• To verify boot code operation.

# Probing the Target System

1. Use an analysis probe to connect the logic analyzer to the microprocessor, and use the provided configuration files to configure the analyzer and define labels.

You may also want to connect an emulation probe to the target system microprocessor's debug port (either via a connector designed into the target system or the connector provided on the analysis probe). The emulation control tool set's reset/run control lets you make this measurement without cycling power in your target system.

#### **Capturing the Data**

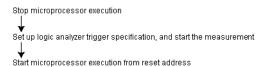

1. Stop microprocessor execution (either by turning OFF power to the target system or using the emulation control tool set's Reset command).

2. Set up a trigger specification to trigger on anything and capture everything.

- 3. Select the Run button to start the measurement.

- 4. Start microprocessor execution from its reset address (either by turning power ON to the target system or by using the emulation control tool set's Reset and Run commands).

## **Displaying the Data**

1. Use the Listing display to show the data that was captured when the target system started up.

See Also

"To start or stop processor execution" on page 147

# Making Driver Development Measurements

- "To trigger on an 8-bit serial pattern" on page 155

- "To view serial data in parallel" on page 160

- "To capture driver execution (& view HW and SW)" on page 165

- "To capture execution up to a failure or halt" on page 171

- "To view bus activity" on page 174

- "To capture simple program messages" on page 175

- "To trigger on packet data (with DataComm Analysis)" on page 177

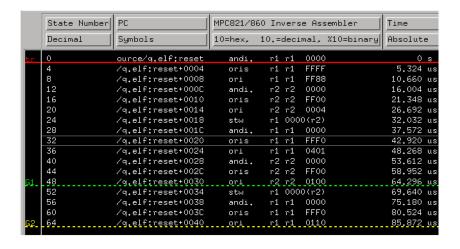

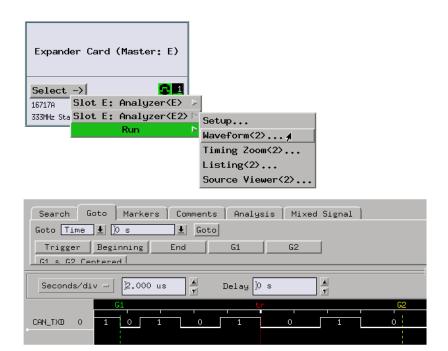

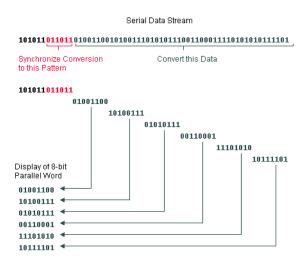

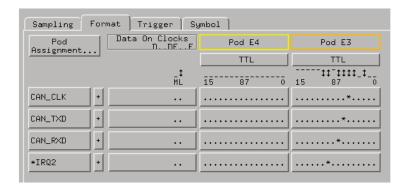

# To trigger on an 8-bit serial pattern

#### Possible uses:

- To view system activity after pattern transmission.

- To look at system status when an error pattern is detected.

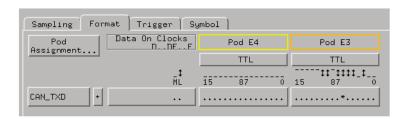

# Probing the Target System

- 1. Connect a logic analyzer probe to the target system's serial signal, and connect the analyzer's clock input probe to the serial transmit/receive clock signal.

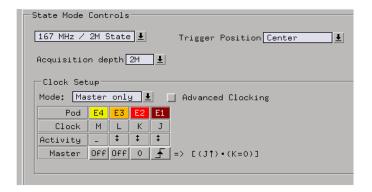

- 2. Configure a state analysis machine and specify the serial transmit/receive clock as the analyzer's clock input.

Or:

Configure a timing analysis machine and make the sample rate the same as

the serial transmit/receive clock.

3. Format a label for the signal on which you will look for the serial pattern.

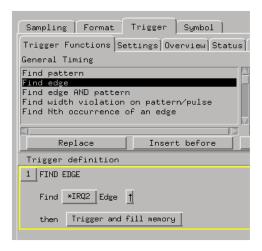

## **Capturing the Data**

1. Set up a trigger sequence where level 1 looks for the first logic level of the pattern; when the pattern is found, level 2 looks for the second logic level of the pattern, etc. If, in each of levels 2 through 8, the appropriate logic

level is not found, branch back to level 1 to start looking for the serial pattern again.

To look look for longer (or shorter) patterns, use more (or fewer) sequence levels.

2. Select the Run button to start the measurement.

# **Displaying the Data**

1. When the analyzer triggers, use the Waveform display to show the 8-bit serial pattern was captured.

If the analyzer never triggers, the serial pattern does not occur. Depending on the level that was reached in the sequence above, you can see how much (or how little) of the pattern was found.

#### See Also

"To view serial data in parallel" on page 160

"If the trigger doesn't occur as expected" on page 309

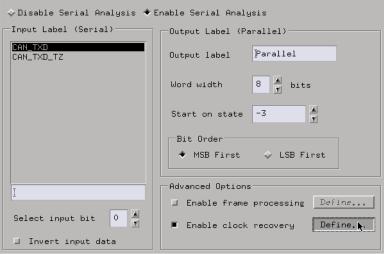

# To view serial data in parallel

# Requirements:

• This measurement requires the serial to parallel tool set.

## Possible uses:

• To view serial data in a format consistent with a particular protocol format.

# Probing the Target System

- 1. Connect a logic analyzer probe to the serial data signal, and connect the serial data transmit (or receive, etc.) clock signal to one of the analyzer's clock input channels.

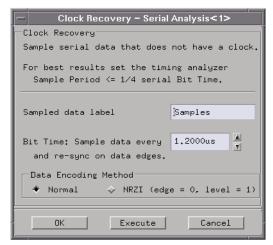

- 2. Configure the logic analyzer as a state analyzer and use the serial transmit/receive clock as the analyzer's clock input.

#### Or:

Configure the analyzer as a timing analyzer and use the Serial To Parallel tool's *Clock Recovery* option.

3. Format a label for the serial data channel.

#### **Capturing the Data**

1. Set up a trigger specification to capture data on the serial channel. You may want to trigger on a particular pattern and capture data that occurs after that pattern.

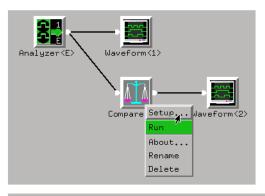

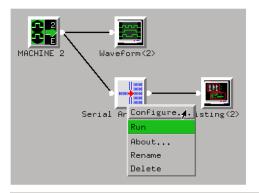

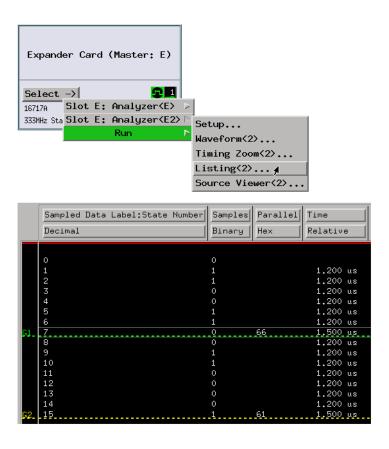

- 2. Configure the measurement workspace so that the logic analyzer feeds the Serial To Parallel tool, which in turn feeds the Listing display.

- 3. Open the Serial To Parallel tool and set up the type of conversion.

4. Select the Run button to start the measurement.

## **Displaying the Data**

1. Open the Listing display window to see the results of the serial to parallel conversion.

See Also

"To trigger on an 8-bit serial pattern" on page 155

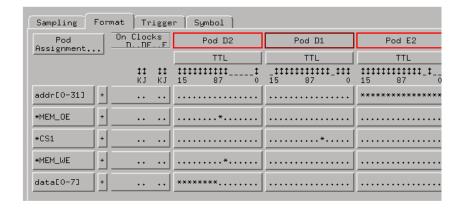

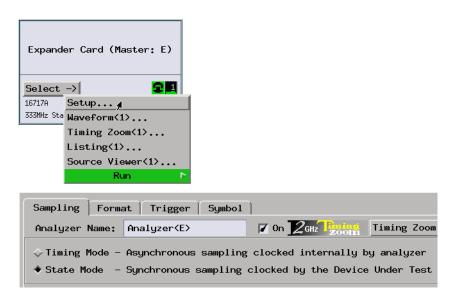

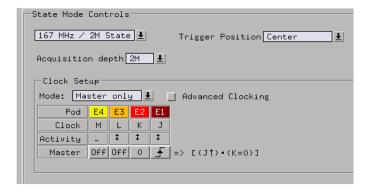

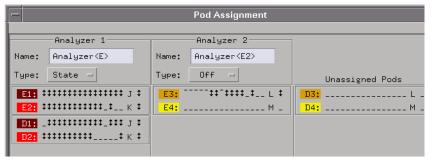

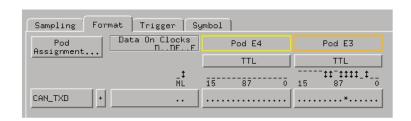

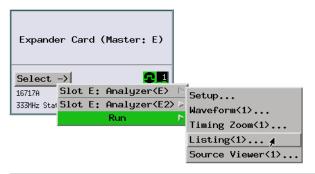

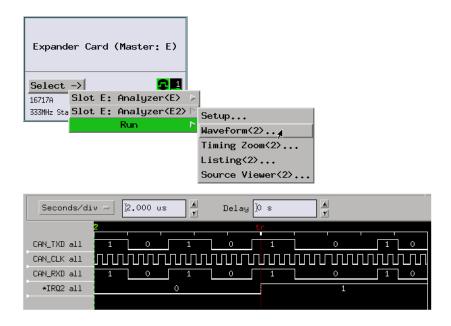

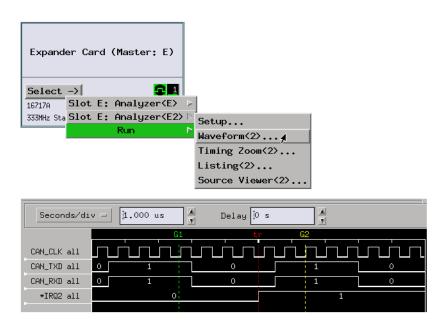

# To capture driver execution (& view HW and SW)

## Possible uses:

To view and correlate driver software execution with hardware signals.

# Probing the Target System

- 1. Probe the microprocessor (using an analysis probe if possible).

- 2. Probe the peripheral with other logic analysis channels (and possibly a probe adapter).

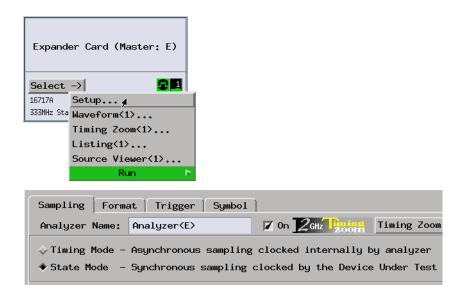

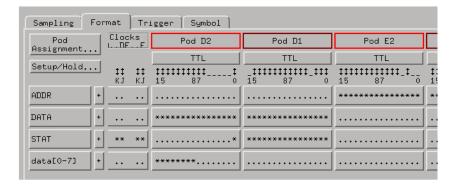

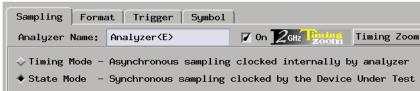

- 3. Configure a state analysis machine.

4. Select the state analyzer's clock input.

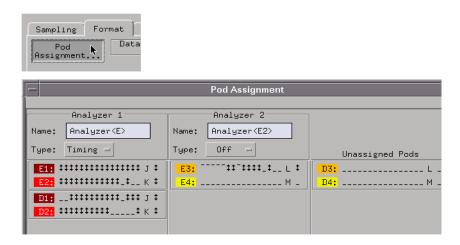

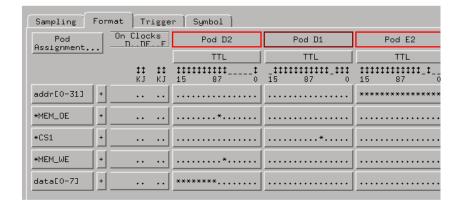

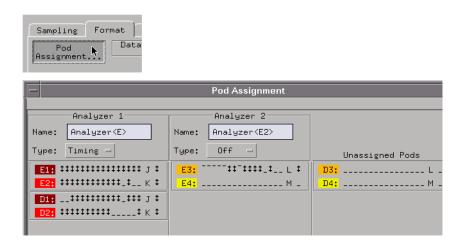

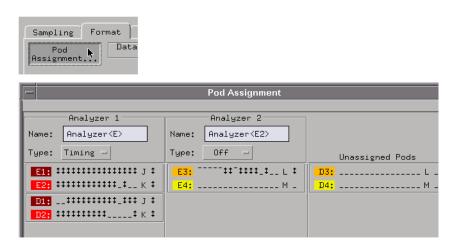

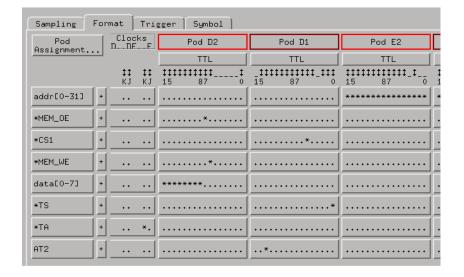

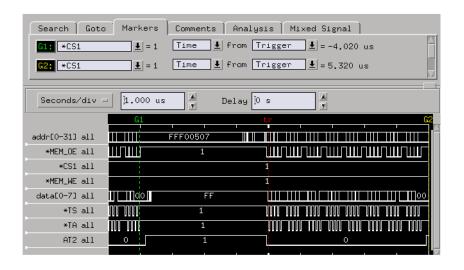

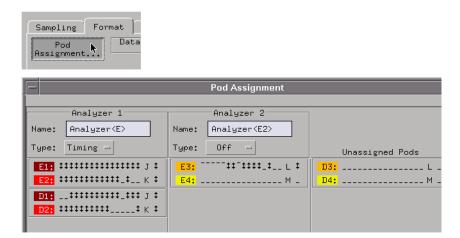

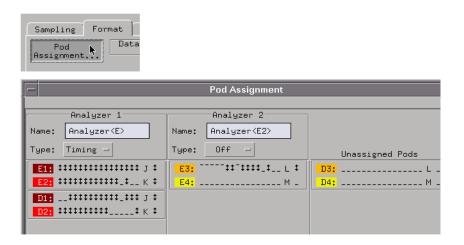

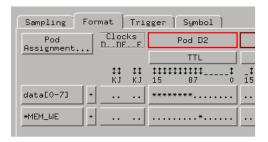

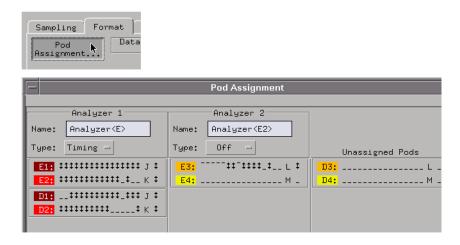

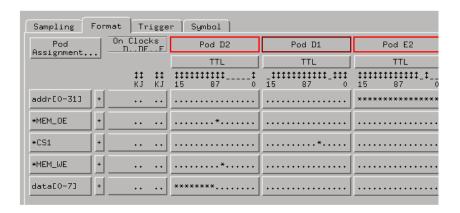

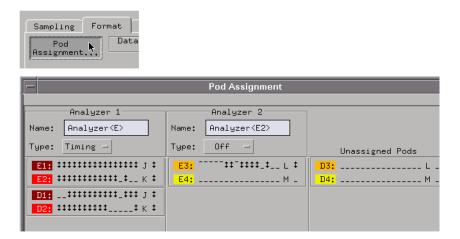

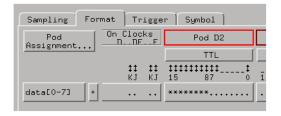

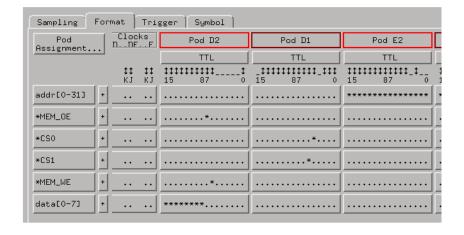

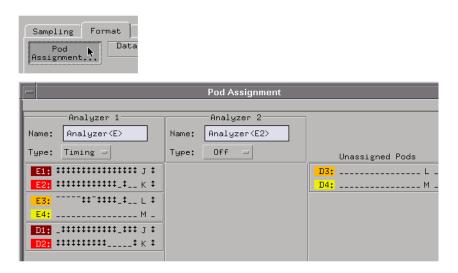

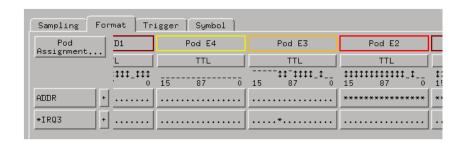

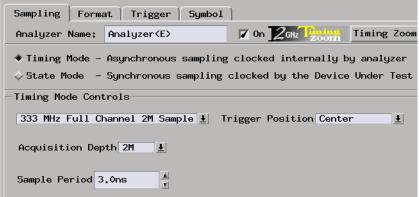

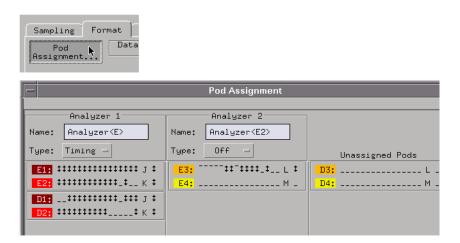

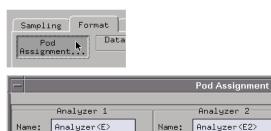

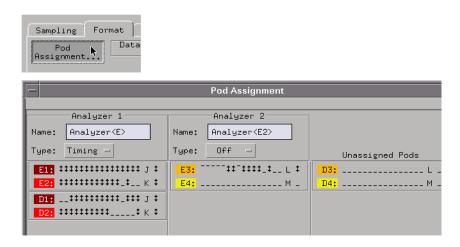

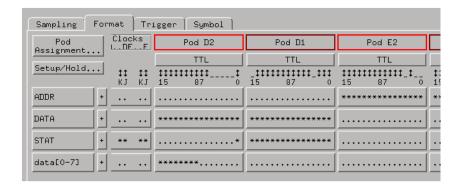

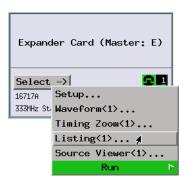

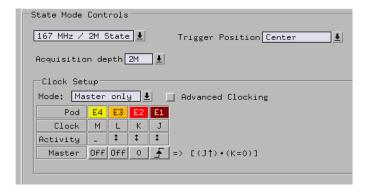

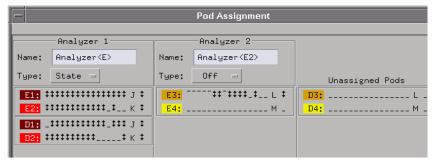

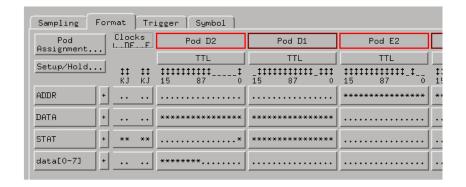

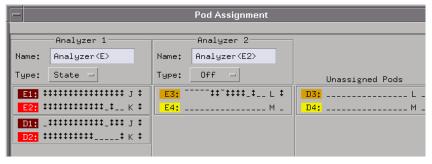

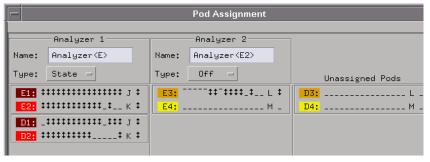

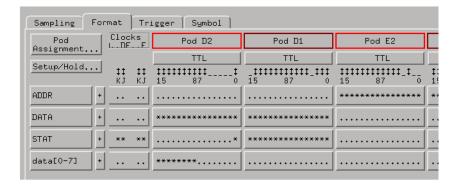

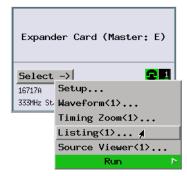

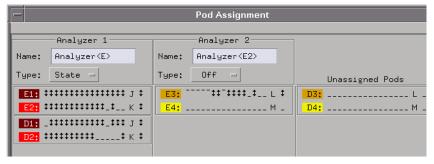

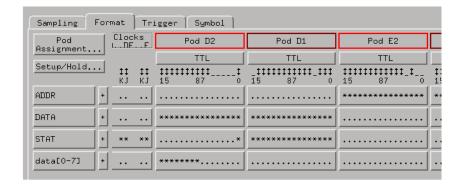

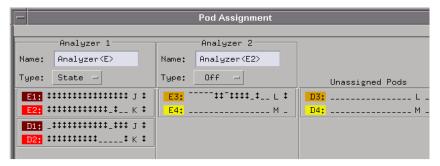

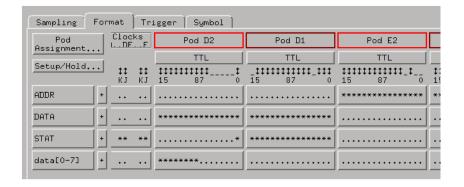

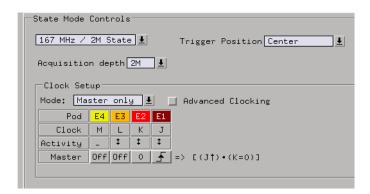

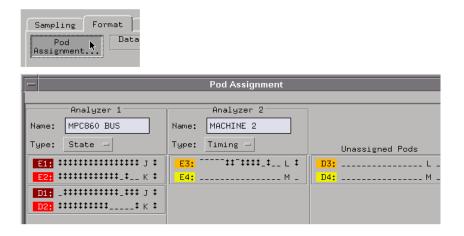

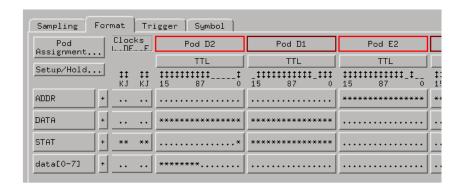

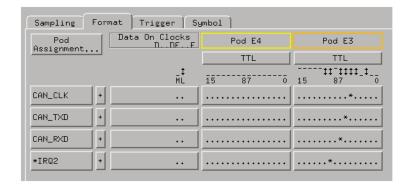

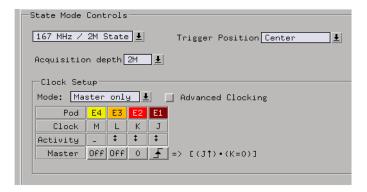

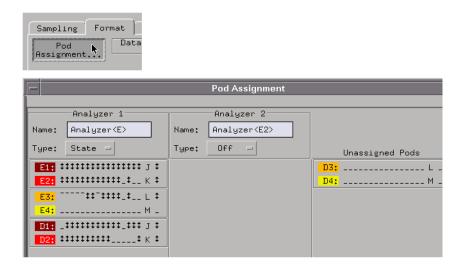

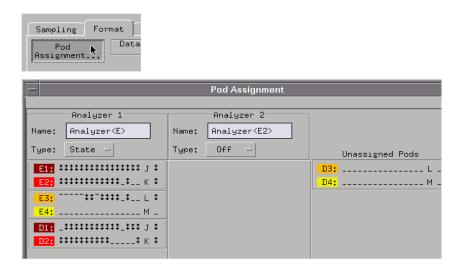

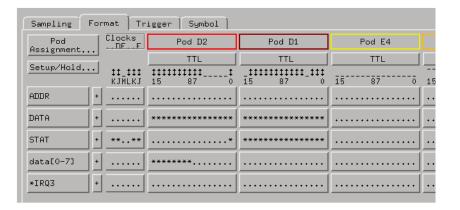

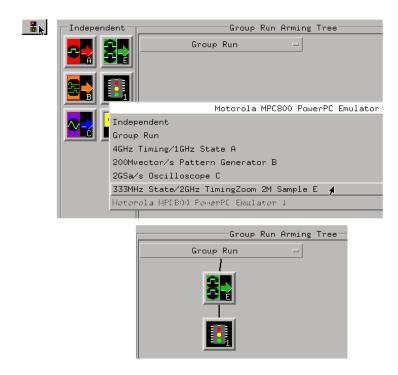

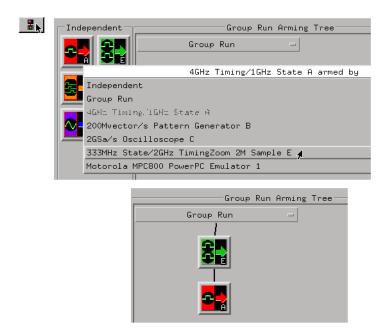

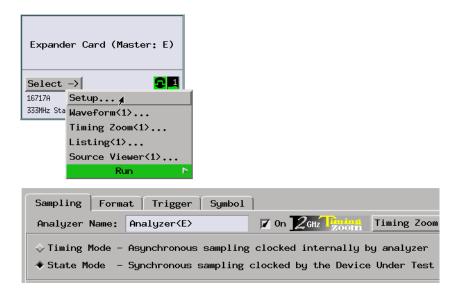

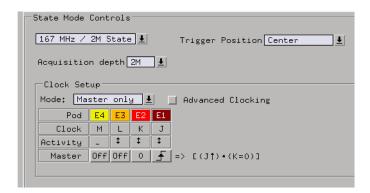

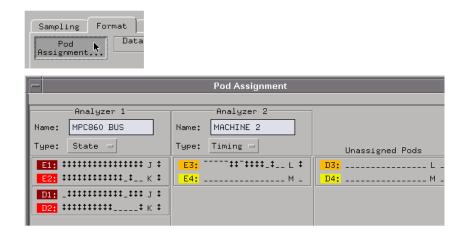

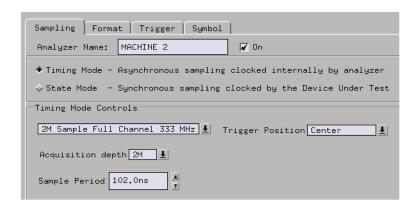

5. Assign pods. Use one logic analyzer machine for analyzing the microprocessor. Create another logic analysis machine for analyzing the peripheral by specifying the Analyzer 2 type.

6. Specify the sampling options for the second logic analyzer machine.

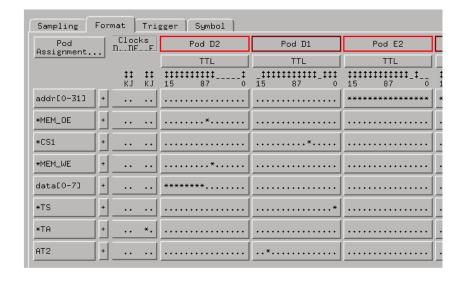

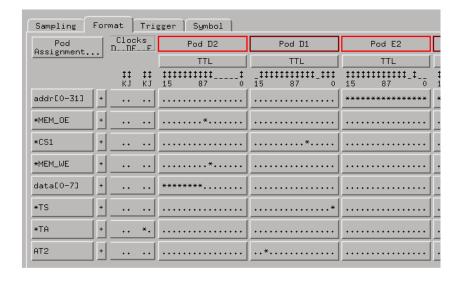

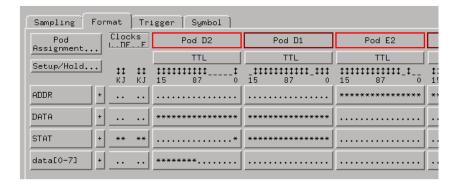

7. Format labels for the signals that are probing the microprocessor.

8. Format labels for the signals that are probing the peripheral.

# **Capturing the Data**

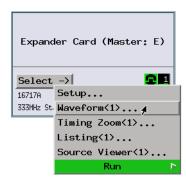

2. Select the Run button to start measurements in each logic analyzer.

# **Displaying the Data**

1. Use the Listing display to show the captured software execution and use the Waveform display to show the captured hardware signals.

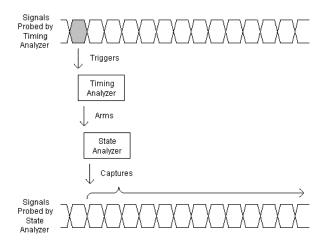

Each analyzer triggers according to its own setup. You can change this by setting up one analyzer to be armed by another analyzer.

See Also

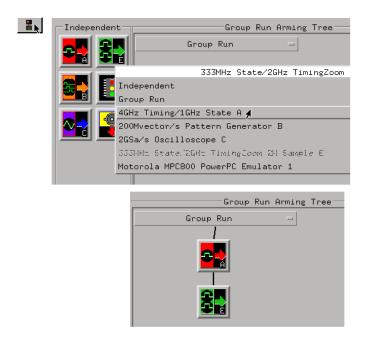

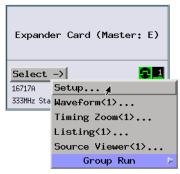

"System Integration" on page 257 for information on coordinating the collection of data with a group run or arming a measurement in one machine by a trigger in the other.

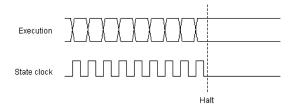

# To capture execution up to a failure or halt

## Possible uses:

• To store and display all activity leading up to a system crash.

• To run the logic analyzer indefinitely until the Stop button is selected so that you can observe system activity at your discretion.

# Probing the Target System

1. Configure a state analysis machine.

2. Select the state analyzer's clock input.

3. Format labels for the signals on which you will look for the event.

## **Capturing the Data**

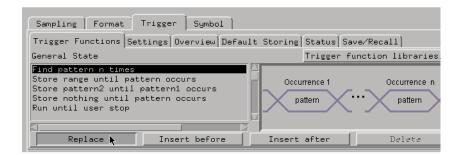

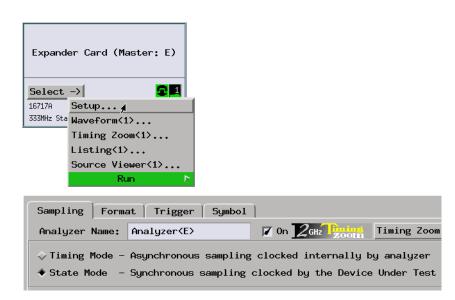

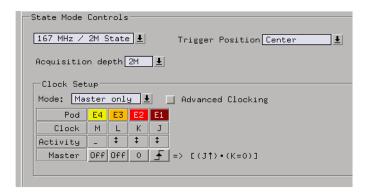

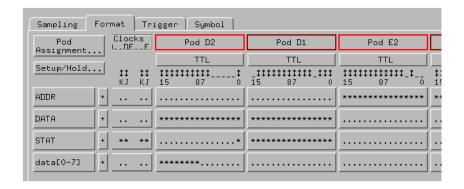

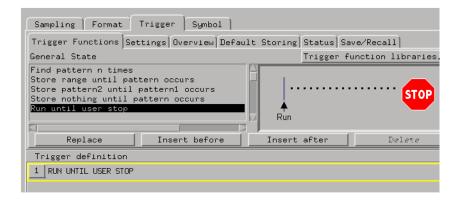

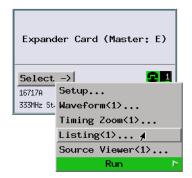

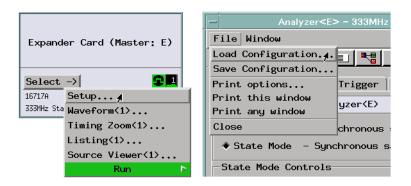

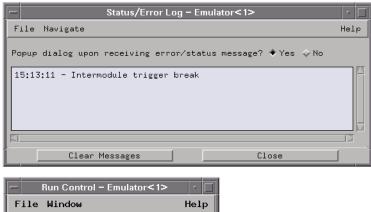

1. Use the "Run until user stop" trigger function.

- 2. Select the Run button to start the measurement.

- 3. When the system fails, crashes, or halts, select the Stop button to see the states that were captured before the failure.

## **Displaying the Data**

1. Use the Listing display to show the states that led up to the failure.

# To view bus activity

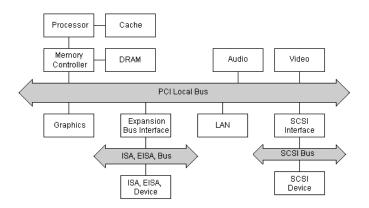

Target system buses are good locations to view system activity and may be the first place you look when isolating problems (especially in multiprocessor systems).

# Requirements:

This measurement requires an analysis probe for the standard bus you wish to view.

#### Possible uses:

- To isolate system problems.

- To view and correlate activity on multiple buses.

- To view and correlate bus activity to microprocessor execution.

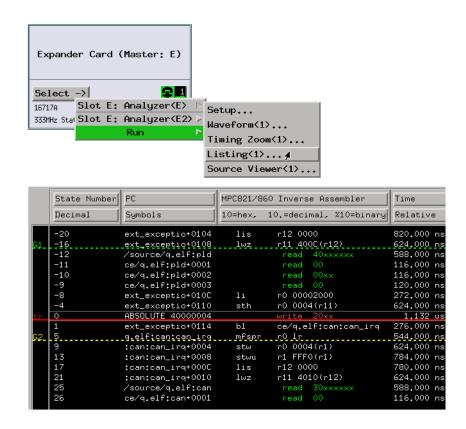

# Probing the Target System

- 1. Use a standard bus analysis probe to make the physical connection between the logic analyzer and the bus.

- 2. Use the configuration files included with the analysis probe to configure the analyzer and format labels.

# **Capturing the Data**

1. Set up a trigger specification using the labels defined by the analysis probe configuration files.

#### Displaying the Data

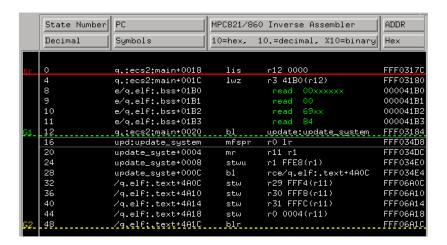

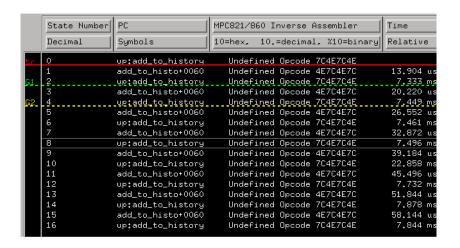

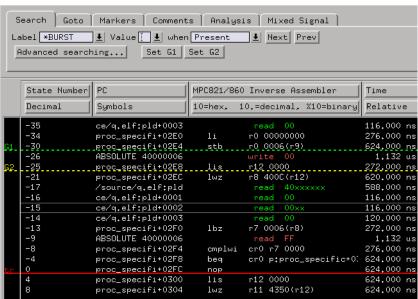

1. Use the Listing display to view captured bus activity. If the standard bus analysis probe provides an inverse assembler, you will see mnemonics for

bus commands, status, etc.

#### See Also

"To analyze bus stability (with SPA)" on page 88

"To analyze bus occupation & bandwidth (with SPA)" on page 131

"To simulate bus occupation and measure SW performance" on page 287

# To capture simple program messages

By adding program code that causes activity external to the processor (also known as "instrumenting your code"), you can create specific program message events that can be captured by the analyzer.

#### Possible uses:

- To view processor execution when the instruction cache is turned ON.

- To view higher-level program activity (like Real-Time OS function calls or OS calls).

# Probing the Target System

1. Typically, you will use an analysis probe to connect the logic analyzer to the microprocessor, and you will use the provided configuration files to configure the analyzer and define labels.

## Capturing the Data

1. Set up a trigger specification and use storage qualifiers that capture the program messages you have coded into your programs.

2. Select the Run button to start the measurement.

## **Displaying the Data**

1. Use the Listing display to view the captured program messages.

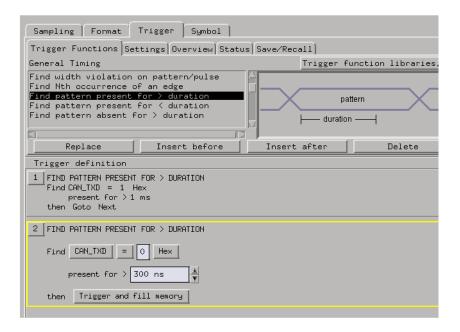

# To trigger on packet data (with DataComm Analysis)

# Requirements:

- The DataComm Analysis tool set.

- An Agilent Technologies 16715/16/17/18/19A logic analyzer module (and its VisiTrigger capabilities).

#### Possible uses:

To look at data traveling across parallel buses inside network switching systems.

# Probing the Target System

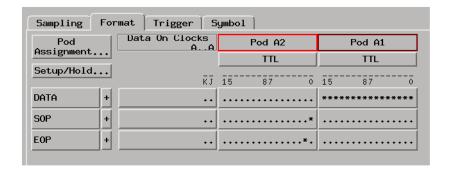

- 1. Connect logic analyzer probe channels to:

- A communication data bus.

- Control signals that identify the start of packet, the packet data, and the end of packet.

- 2. You also need to connect a logic analyzer CLK input channel to:

- A clock signal that identifies when the data bus and control signals are valid and should be sampled by the logic analyzer.

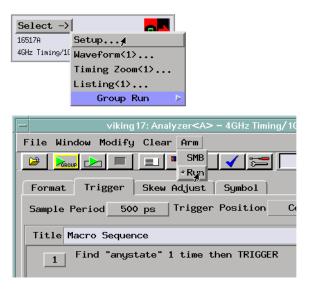

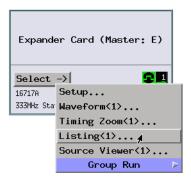

- 3. Configure a (synchronous sampling) state analysis machine.

4. Select the state analyzer's clock input.

5. Format a DATA label for the logic analyzer channels that are probing the data bus. Format 1-bit labels for the channels that are probing the start of packet, packet data, and end of packet signals.

## **Capturing the Data**

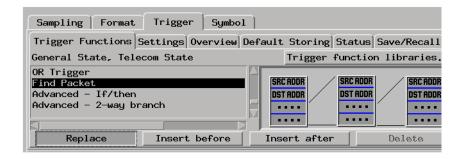

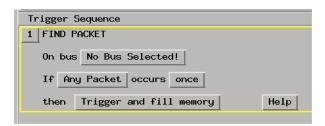

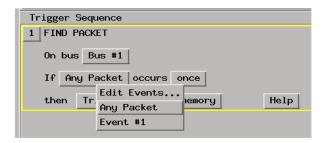

1. Select the "Find Packet" trigger function.

- 2. In the "Find Packet" trigger sequence level, select the bus button.

- 3. In the Bus Selector dialog, select the bus definition you want to use and select the OK button.

4. Specify the packet event to find.

5. Select the Run button to start the measurement.

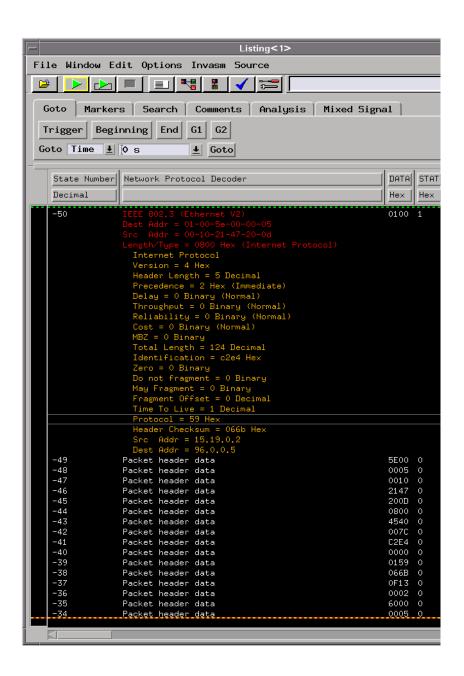

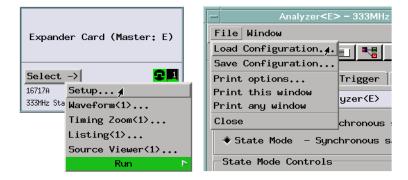

# **Displaying the Data**

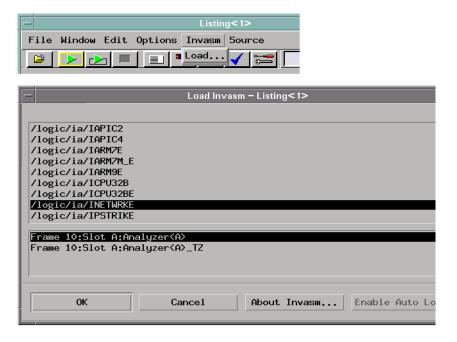

1. In the logic analyzer's Listing window, load the INETWRKE network protocol decoder inverse assembler.

2. View the captured data.

See Also

Using the DataComm Analysis Toolset (see the DataComm Analysis

Toolset help volume)

# Making Interrupt Service Routine Measurements

- "To capture interrupt frequency and type" on page 183

- "To measure interrupt latency and execution time" on page 186

- "To simulate particular interrupt sequences" on page 191

- "To view the occurrence rate of an event (with SPA)" on page 192

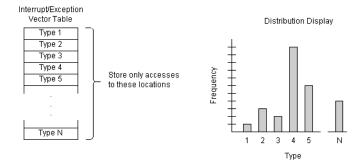

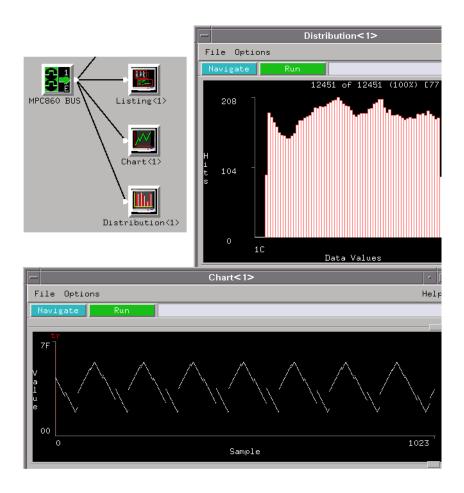

# To capture interrupt frequency and type

#### Possible uses:

To analyze interrupt processing.

# Probing the Target System

1. Typically, you will use an analysis probe to connect the logic analyzer to the microprocessor, and you will use the provided configuration files to configure the analyzer and define labels.

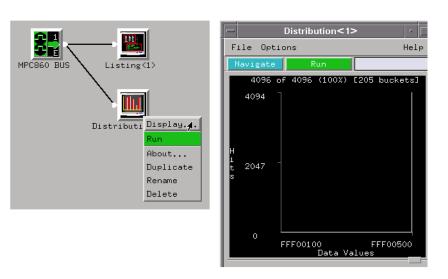

#### **Capturing the Data**

1. The trigger specification will depend on the interrupt mechanism of your microprocessor.

If your processor uses an interrupt vector table, set up a trigger specification that only stores accesses to the interrupt vector table locations.

2. Select the Run button to start the measurement.

### **Displaying the Data**

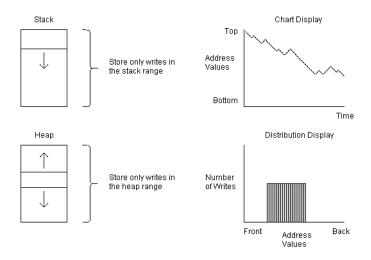

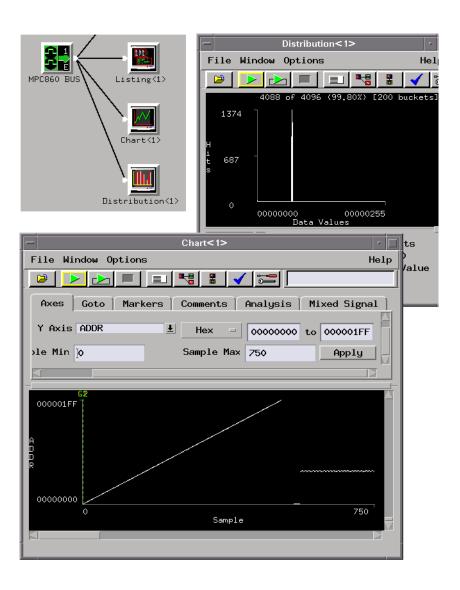

1. In the Workspace window, add the Distribution display to view the captured data.

If your trigger specification stored interrupt vector table accesses, the captured table locations will show the interrupt types.

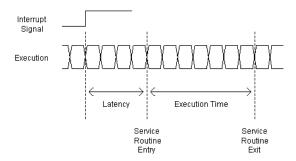

# To measure interrupt latency and execution time

#### Possible uses:

To see if interrupt processing meets specifications.

# Probing the Target System

1. Configure a state analysis machine.

2. Select the state analyzer's clock input.

3. Assign pods if necessary.

4. Format labels for the signals on which you will look for the event.

# **Capturing the Data**

1. Set up a trigger specification that stores the state when the interrupt signal becomes active, the interrupt service routine entry point, and the interrupt routine exit point.

- 2. Make sure the analyzer is counting time.

- 3. Select the Run button to start the measurement.

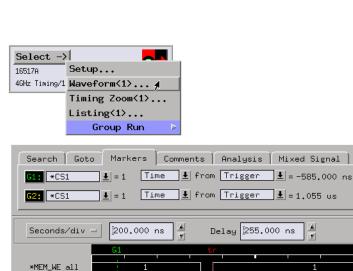

## **Displaying the Data**

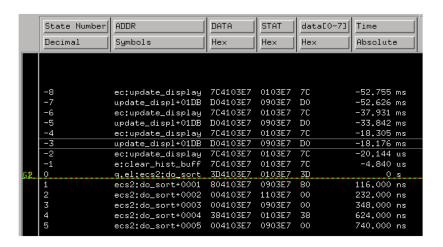

1. Use the Listing display to view the captured states.

The relative time between the state where the interrupt signal became active and the service routine entry shows the interrupt latency.

The relative time between the service routine entry and exit shows the interrupt execution time.

See Also

"To measure function execution time (with SPA)" on page 218

# To simulate particular interrupt sequences

## Requirements:

• This measurement requires a pattern generator module (Agilent Technologies 16522A).

#### Possible uses:

• To test the processing of multiple interrupts.

#### Probing the Target System

- 1. Connect pattern generator outputs to microprocessor interrupt inputs.

- 2. Configure the pattern generator to output the desired sequence of interrupt signals.

- 3. Typically, you will use an analysis probe to connect the logic analyzer to the microprocessor, and you will use the provided configuration files to configure the analyzer and define labels.

#### **Capturing the Data**

1. Set up the trigger specification to capture the interrupt processing.

## **Displaying the Data**

1. Use the Listing display to view the captured interrupt processing.

#### See Also

"To generate pattern stimulus on devices" on page 75

"To generate patterns when a source line executes" on page 262

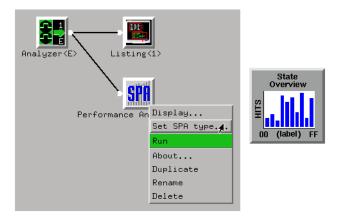

# To view the occurrence rate of an event (with SPA)

#### Requirements:

• This measurement requires the system performance analyzer (SPA) tool set.

## Possible uses:

- To display interrupt loading.

- To measure the frequency at which data is acquired from sensors.

# Probing the Target System

- 1. Connect the logic analyzer to the target system signals on which you will look for the event. You can use an analysis probe to connect the logic analyzer to a microprocessor or standard bus.

- 2. Configure a state analysis machine. (If you are using an analysis probe, use the provided configuration files to configure the analyzer and define labels.)

3. Select the state analyzer's clock input.

4. Assign pods if necessary.

5. Format labels for the signals on which you will look for the event.

## **Capturing the Data**

1. Set up the logic analyzer trigger specification to capture the events you're interested in.

2. Select the Run button to start the measurement.

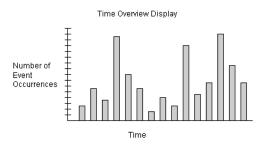

#### **Displaying the Data**

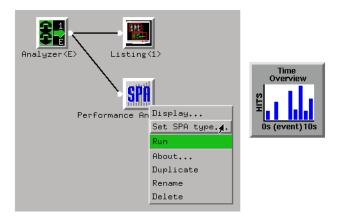

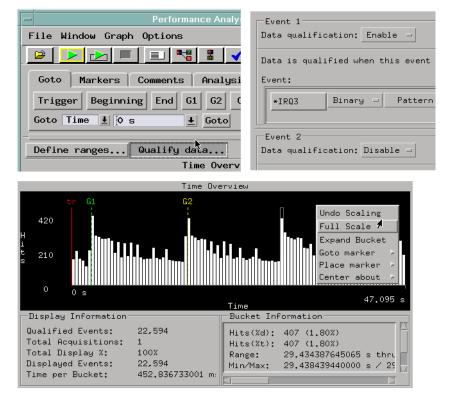

1. Use the system performance analyzer's Time Overview display to show the results of the measurement.

2. Define the event whose occurrence rate you wish to measure.

You can define both the event and the time period in which the events are counted.

# Software Development

Analyzing Real-Time Software Execution

- "To trace about a source line" on page 199

- "To trace function flow" on page 203

- "To trace callers of a function" on page 206

- "To trace execution within a function" on page 210

- "To measure function execution time" on page 214

- "To measure function execution time (with SPA)" on page 218

- "To omit monitor cycles from the trace" on page 223

- "To stop execution at a source line (in ROM)" on page 226

Analyzing Real-Time Variable Access

- "To find NULL pointer de-references" on page 229

- "To trace a variable's values" on page 231

- "To find where variables are accessed from" on page 236

- "To trace before a variable value" on page 240

- "To stop execution on a corrupt variable" on page 245

Analyzing Real-Time Memory Usage

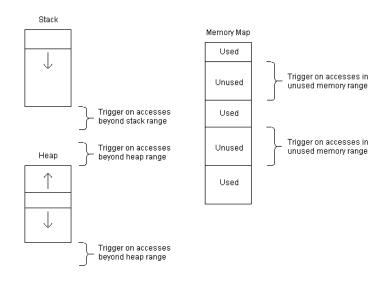

- "To monitor stack or heap usage" on page 251

- "To find stack overflow or guarded memory access" on page 255

# Analyzing Real-Time Software Execution

- "To trace about a source line" on page 199

- "To trace function flow" on page 203

- "To trace callers of a function" on page 206

- "To trace execution within a function" on page 210

- "To measure function execution time" on page 214

- "To measure function execution time (with SPA)" on page 218

- "To omit monitor cycles from the trace" on page 223

- "To stop execution at a source line (in ROM)" on page 226

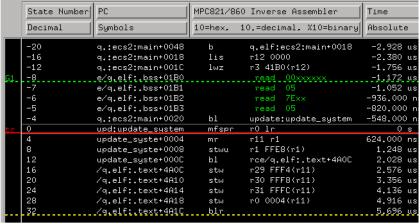

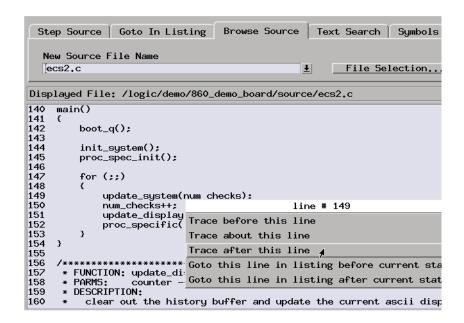

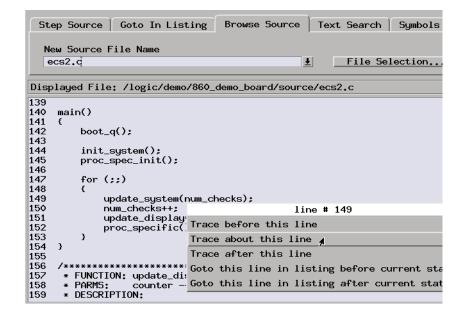

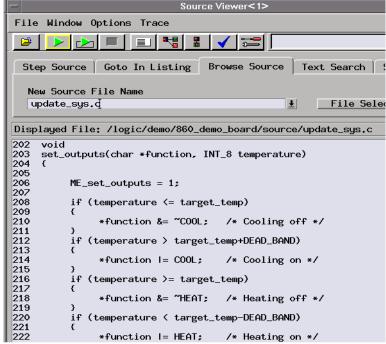

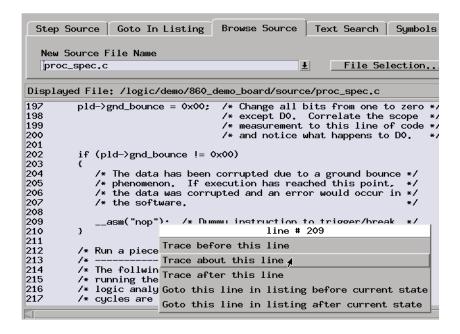

#### To trace about a source line

```

140

141

main()

142

boot_q();

143

144

145

init_system();

proc_spec_init();

146

147

148

for (;;)

149

update_system(num_checks);

150

line # 149

num checks++:

num_checks**;

update_display(num_checks)

Trace before this line

151

152

153

Trace about this line

154

3

155

156

157

158

Trace after this line 🖈

Goto this line in listing before current stat

* FUNCTION: update_display

* PARMS:

counter -- loop count Goto this line in listing after current state

* DESCRIPTION:

```

#### Requirements:

• This measurement requires the source correlation tool set product. When this product is installed, you can view high-level source files in a special listing window.

#### Possible uses:

To quickly capture and view execution around a particular high-level source line.

# Probing the Target System

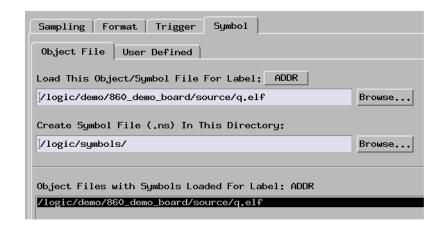

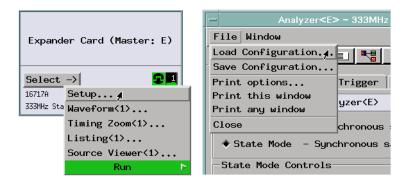

1. Use an analysis probe to connect the logic analyzer to the microprocessor, and use the provided configuration files to configure the analyzer and define labels.

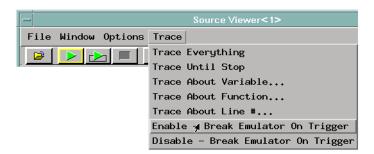

## **Capturing the Data**

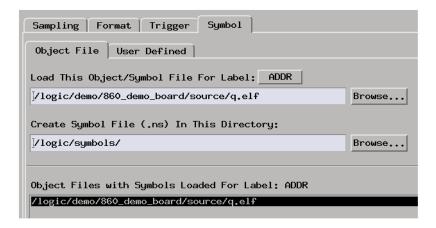

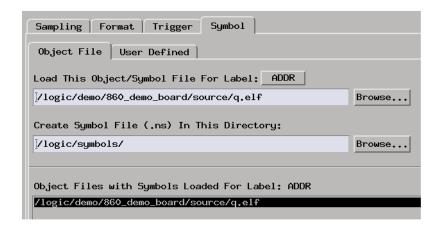

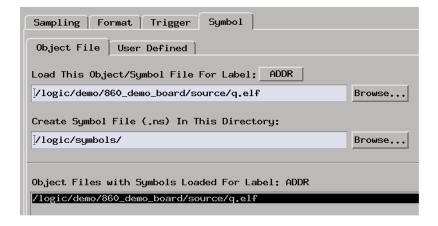

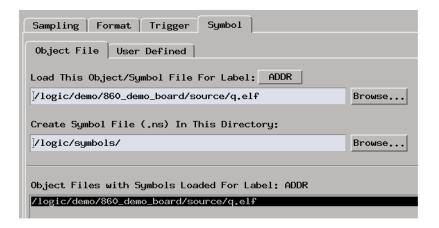

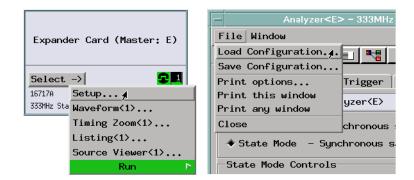

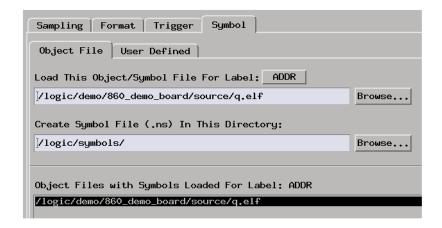

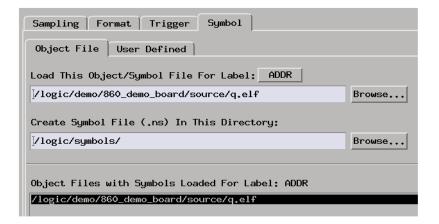

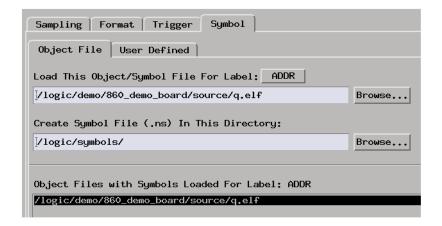

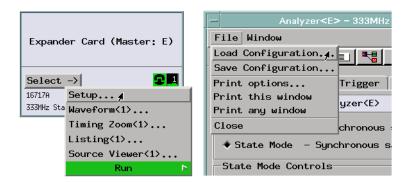

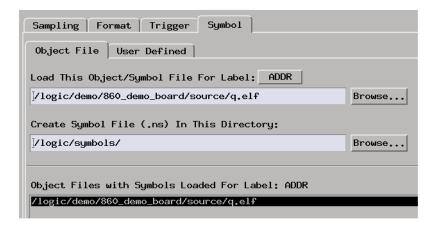

1. Download symbols from your target system program's object module file.

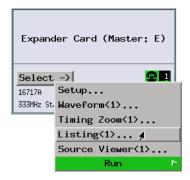

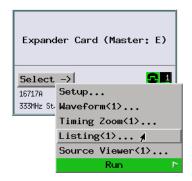

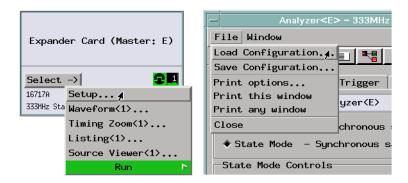

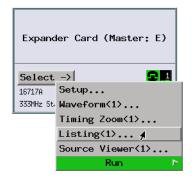

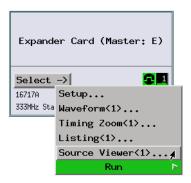

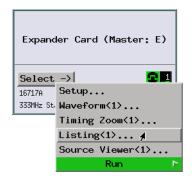

2. Open the Source Viewer window.

- 3. Browse the source file that contains the line you want to trigger on.

- 4. Select the line you want to trigger on and choose the "Trigger after this line" menu item.

#### NOTE:

Source Viewer commands that set up triggers only modify the trigger condition. They do not modify the trigger position, storage qualifiers, else branch conditions, or other levels in the trigger sequence.

## **Software Development**

5. Select the Run button to start the measurement.

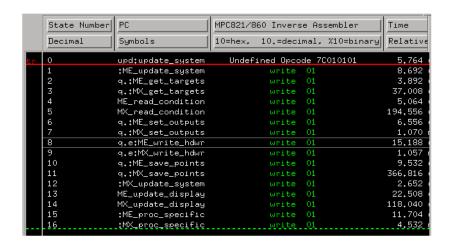

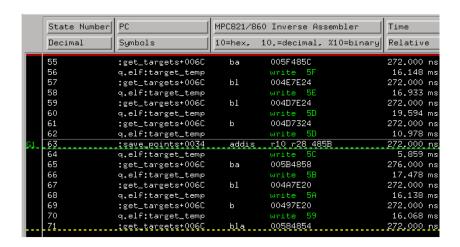

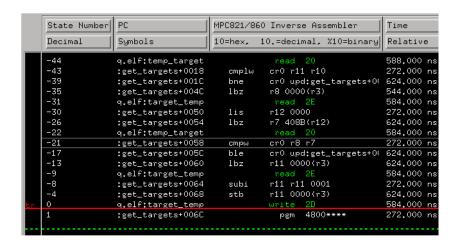

#### **Displaying the Data**

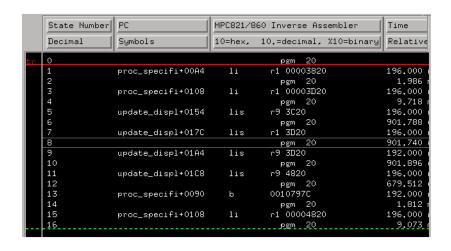

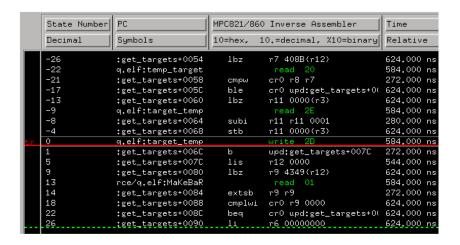

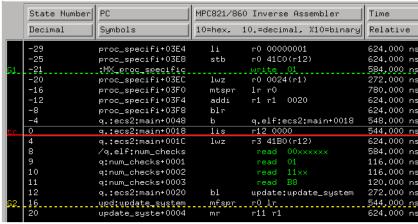

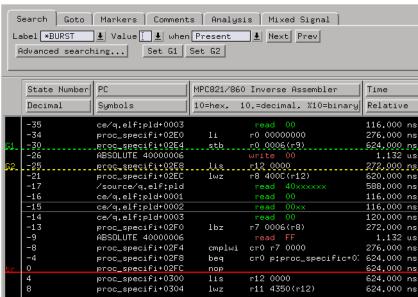

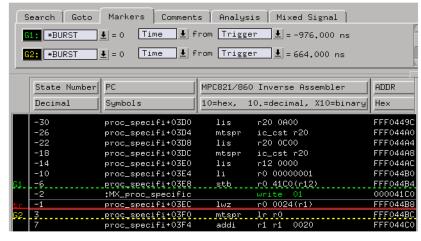

1. Open the Listing window to display the captured data. You may want to load an inverse assembler and display symbols in the address label column.

2. You can use the Step Source Previous and Next buttons in the Source Viewer window to browse the captured data by associated source lines.

#### See Also

"To stop execution at a source line (in ROM)" on page 226

"To generate patterns when a source line executes" on page 262

"To trigger an oscilloscope when a source line executes" on page 294

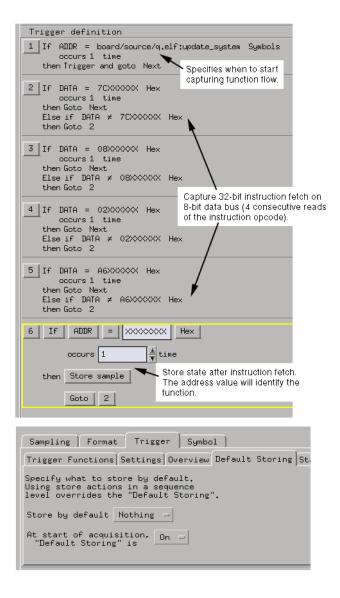

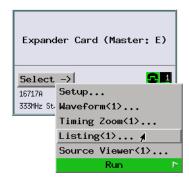

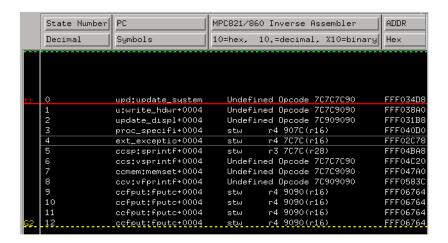

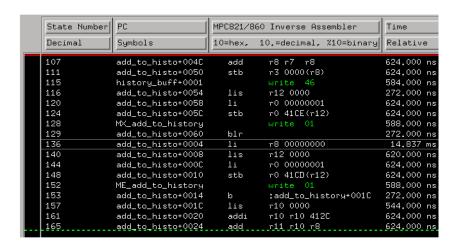

## To trace function flow

#### Possible uses:

• To view the execution order of routines.

# Probing the Target System

1. Use an analysis probe to connect the logic analyzer to the microprocessor, and use the provided configuration files to configure the analyzer and define labels.

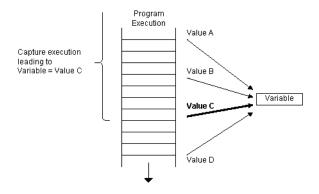

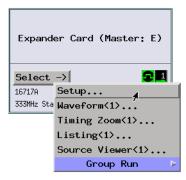

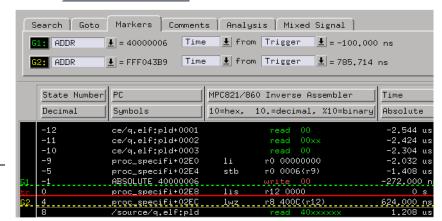

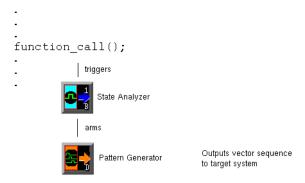

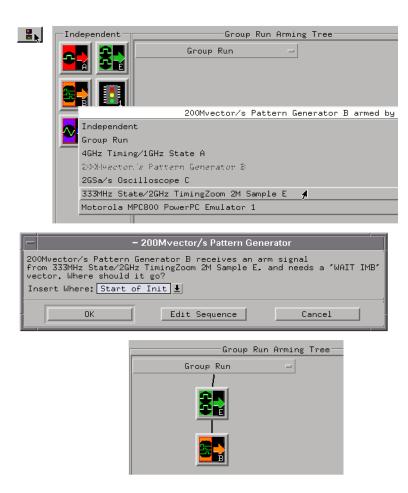

2. Load symbols from your program's object module file.